# **ARM Low-power Processors** and Architectures

rld® The Architecture for the

the Digital Wor

**Dan Millett** Verification Enablement **Processor Division**

# Agenda

### Introduction to ARM Ltd

**ARM Architecture/Programmers Model**

- **Data Path and Pipelines**

- System Design

- **Development Tools**

# ARM Ltd

- Founded in November 1990

- Spun out of Acorn Computers

- Initial funding from Apple, Acorn and VLSI

- Designs the ARM range of RISC processor cores

- Licenses ARM core designs to semiconductor partners who fabricate and sell to their customers

- ARM does not fabricate silicon itself

- Also develop technologies to assist with the designin of the ARM architecture

- Software tools, boards, debug hardware

- Application software

- Bus architectures

- Peripherals, etc

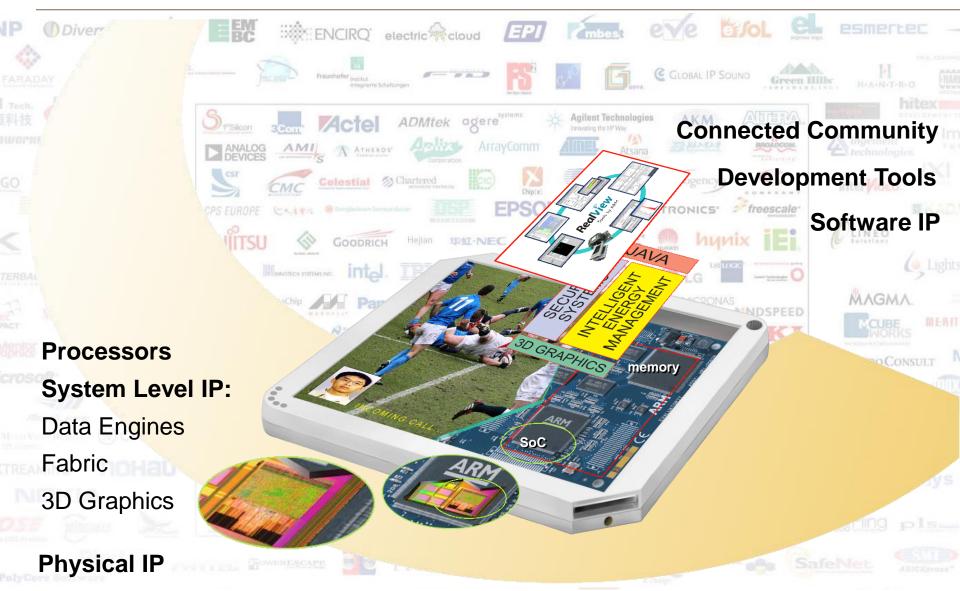

# **ARM's Activities**

# **ARM Connected Community – 700+**

#### Silicon Partners

#### Design Support Partners

MXIC anoradio

# **Huge Range of Applications**

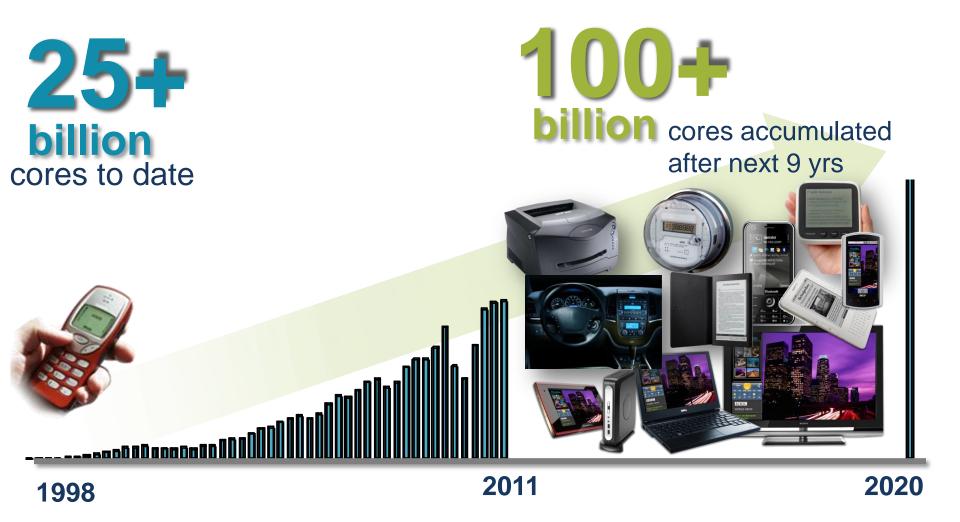

# How many ARM's Do You Have?

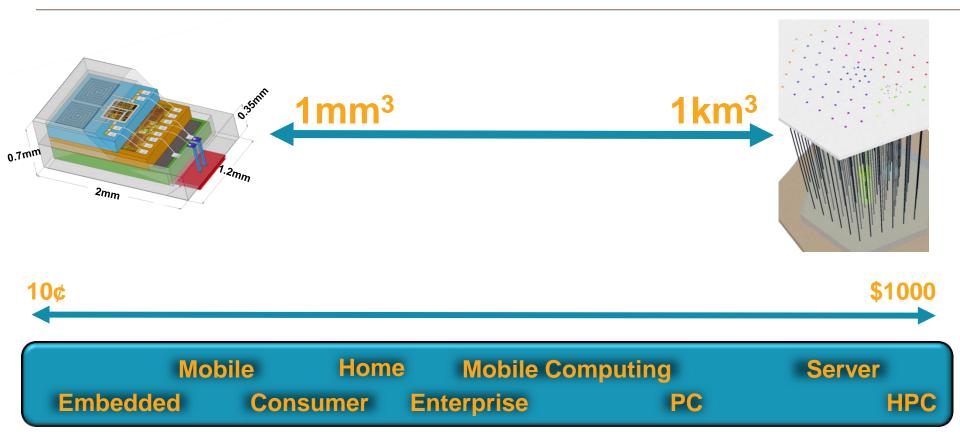

# **Huge Opportunity For ARM Technology**

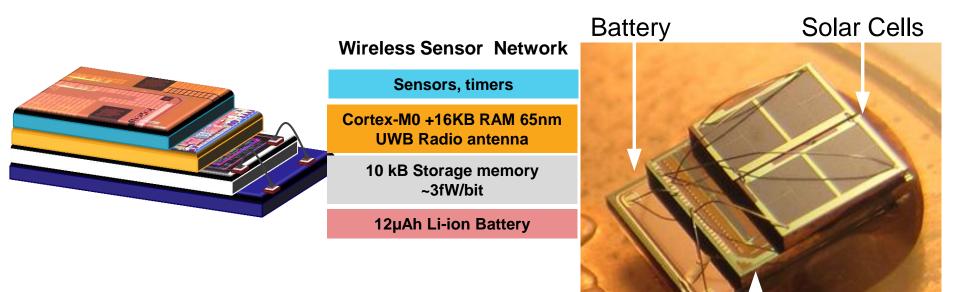

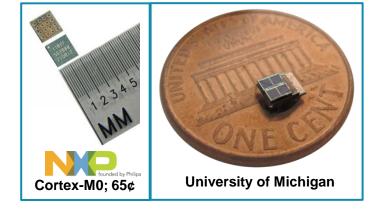

# World's Smallest ARM Computer?

Processor, SRAM and PMU

### Wirelessly networked into large scale sensor arrays

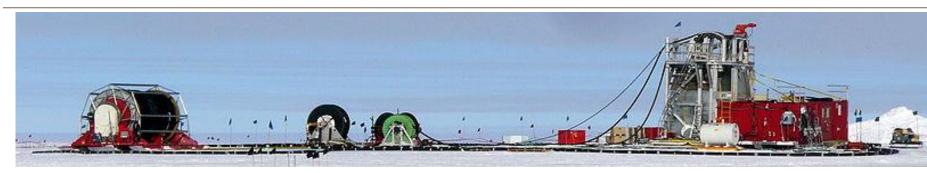

# World's Largest ARM Computer?

4200 ARM powered Neutrino Detectors

70 bore holes 2.5km deep

60 detectors per string starting 1.5km down 2.5km

1km<sup>3</sup> of active telescope

ARM

# From 1mm<sup>3</sup> to 1km<sup>3</sup>

# Agenda

Introduction to ARM Ltd

ARM Architecture/Programmers Model

Data Path and Pipelines System Design Development Tools

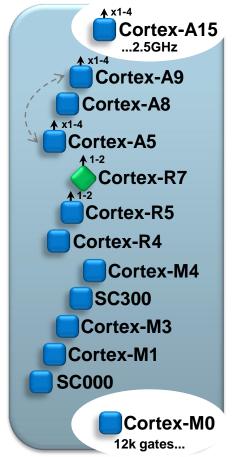

# **ARM Cortex Advanced Processors**

### ARM Cortex-A family:

- Applications processors

- Targeted for OS's, graphics, demanding tasks

### ARM Cortex-R family:

- Embedded processors

- Real-time signal processing, control applications

### ARM Cortex-M family:

- Microcontroller-oriented processors

- MCU, ASSP, and SoC applications

## **Relative Performance\***

\*Represents attainable speeds in 130, 90, 65, or 45nm processes

# **Cortex family**

#### **Cortex-A8**

- Architecture v7A

- MMU

- AXI

- VFP & NEON support

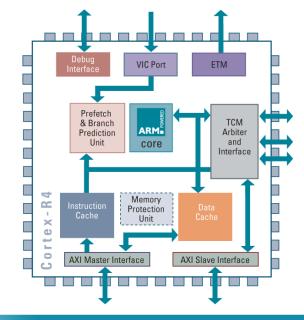

#### Cortex-R4

- Architecture v7R

- MPU (optional)

- AXI

- Dual Issue

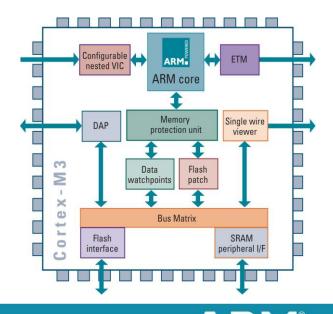

#### Cortex-M3

- Architecture v7M

- MPU (optional)

- AHB Lite & APB

# **Data Sizes and Instruction Sets**

- The ARM is a 32-bit architecture.

- When used in relation to the ARM:

- Byte means 8 bits

- Halfword means 16 bits (two bytes)

- Word means 32 bits (four bytes)

- Most ARM's implement two instruction sets

- 32-bit ARM Instruction Set

- 16-bit Thumb Instruction Set

- Jazelle cores can also execute Java bytecode

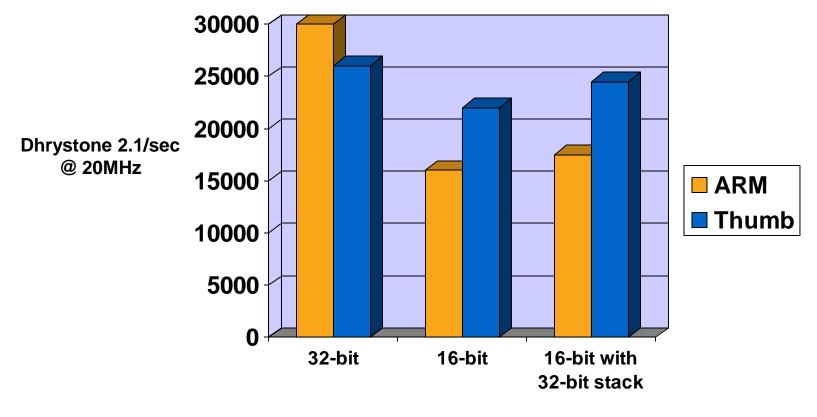

## **ARM and Thumb Performance**

Memory width (zero wait state)

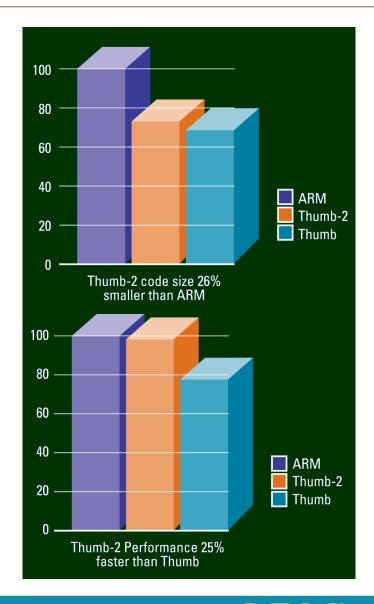

# The Thumb-2 instruction set

- Variable-length instructions

- ARM instructions are a fixed length of 32 bits

- Thumb instructions are a fixed length of 16 bits

- Thumb-2 instructions can be either 16-bit or 32-bit

- Thumb-2 gives approximately 26% improvement in code density over ARM

- Thumb-2 gives approximately 25% improvement in performance over Thumb

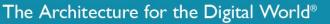

## **Processor Modes**

- The ARM has seven basic operating modes:

- User : unprivileged mode under which most tasks run

- FIQ : entered when a high priority (fast) interrupt is raised

- IRQ : entered when a low priority (normal) interrupt is raised

- Supervisor : entered on reset and when a Software Interrupt instruction is executed

- Abort : used to handle memory access violations

- Undef : used to handle undefined instructions

- System : privileged mode using the same registers as user mode

# **The ARM Register Set**

### **Current Visible Registers**

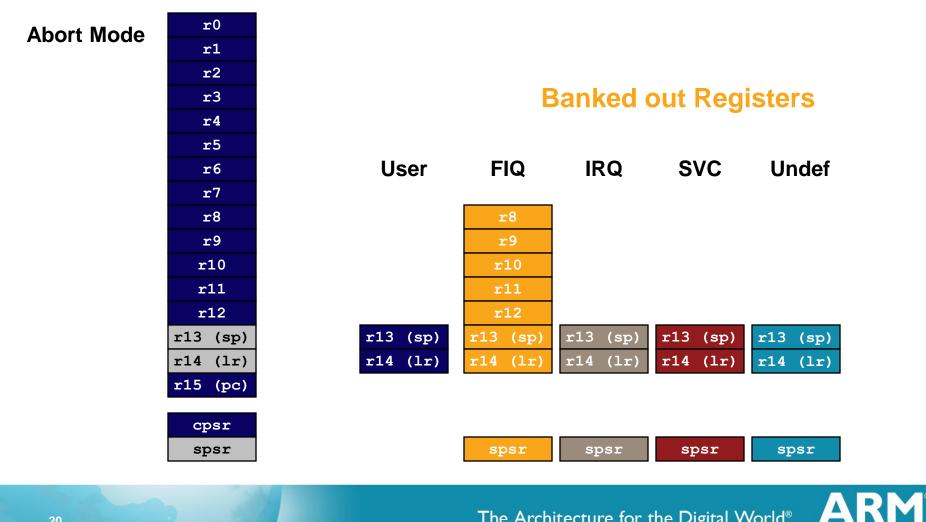

# **Program Status Registers**

- Condition code flags

- N = Negative result from ALU

- Z = Zero result from ALU

- C = ALU operation Carried out

- V = ALU operation oVerflowed

- Sticky Overflow flag Q flag

- Architecture 5TE/J only

- Indicates if saturation has occurred

- J bit

- Architecture 5TEJ only

- J = 1: Processor in Jazelle state

- Interrupt Disable bits.

- I = 1: Disables the IRQ.

- F = 1: Disables the FIQ.

### T Bit

- Architecture xT only

- T = 0: Processor in ARM state

- T = 1: Processor in Thumb state

- Mode bits

- Specify the processor mode

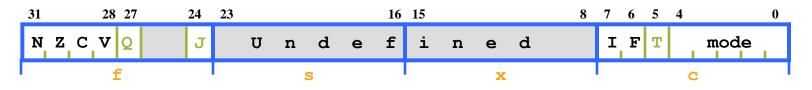

# **Conditional Execution and Flags**

- ARM instructions can be made to execute conditionally by postfixing them with the appropriate condition code field.

- This improves code density and performance by reducing the number of forward branch instructions.

| CMP  | r3,#0    |

|------|----------|

| BEQ  | skip     |

| ADD  | r0,r1,r2 |

| skip | <b>—</b> |

CMP r3,#0 ADDNE r0,r1,r2

By default, data processing instructions do not affect the condition code flags but the flags can be optionally set by using "S". CMP does not need "S".

loop

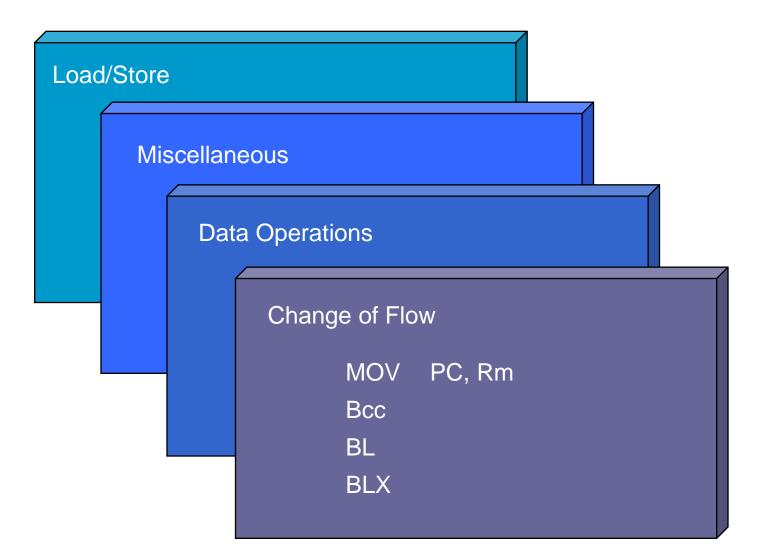

### **Classes of Instructions**

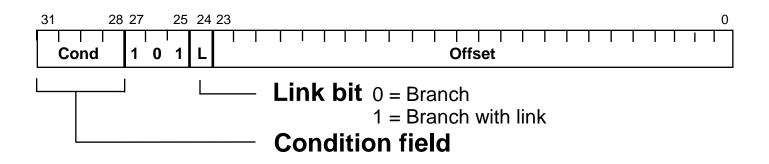

# **Branch instructions**

- Branch: B{<cond>} label

- Branch with Link : BL{<cond>} subroutine\_label

- The processor core shifts the offset field left by 2 positions, sign-extends it and adds it to the PC

- ± 32 Mbyte range

- How to perform longer branches?

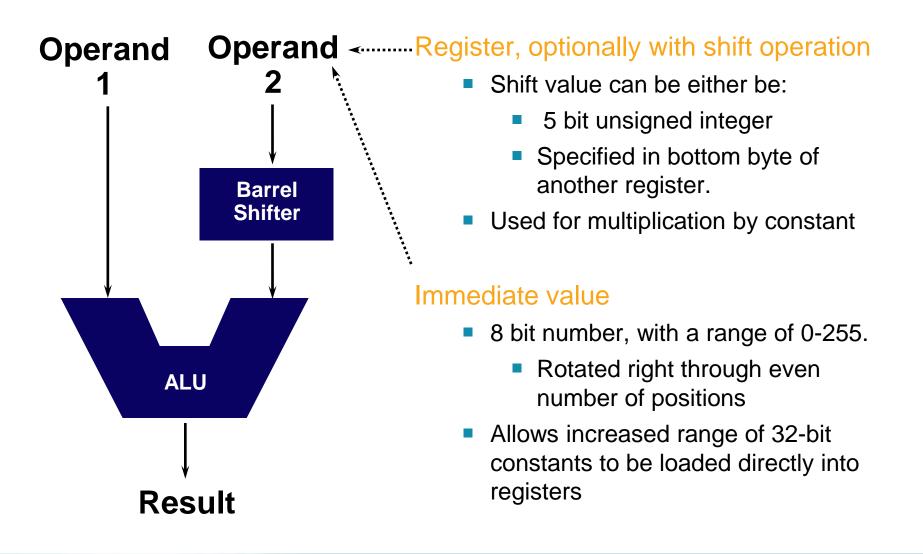

# **Data processing Instructions**

### Consist of :

| Arithmetic:  | ADD | ADC | SUB | SBC | RSB | RSC |

|--------------|-----|-----|-----|-----|-----|-----|

| Logical:     | AND | ORR | EOR | BIC |     |     |

| Comparisons: | CMP | CMN | TST | TEQ |     |     |

- Data movement: MOV MVN

- These instructions only work on registers, NOT memory.

- Syntax:

<Operation>{<cond>}{S} Rd, Rn, Operand2

- Comparisons set flags only they do not specify Rd

- Data movement does not specify Rn

- Second operand is sent to the ALU via barrel shifter.

# Using a Barrel Shifter: The 2nd Operand

# **Data Processing Instruction Examples**

| ■ MOV r3, r0      | ; copies r0 into r3                        |

|-------------------|--------------------------------------------|

| ■ MVN r6, r8      | ; copies the complement of r8 into r6      |

| ■ ADD r0, r1, r2  | ; r0 = r1 + r2                             |

| ■ ADC r0, r1, r2  | ; r0 = r1 + r2 + <carry flag=""></carry>   |

| ■ SUB r3, r1, r7  | ; r3 = r1 - r7                             |

| ■ RSB r3, r1, r7  | ; r3 = r7 - r1                             |

| ■ SBC r3, r1, r7  | ; r3 = r1 - (r7 + <carry flag="">)</carry> |

|                   |                                            |

| AND r0, r1, #0xA5 | ; r0 = r1 & 0xA5                           |

| BIC r0, r1, #0xA5 | ; $r0 = r1$ with bits 0,2,5,and 7 cleared  |

| ORR r0, r1, #0xA5 | ; $r0 = r1$ with bits 0,2,5,and 7 set      |

|                   |                                            |

| ■ CMP r5, r9      | ; same as SUBS, but only affects APSR      |

| CMN r0, r1        | ; same as ADDS, but only affects APSR      |

| ■ TST r0, r1      | ; same as ANDS, but only affects APSR      |

| ■ TEQ r0, r1      | ; same as EORS, but only affects APSR      |

The Architecture for the Digital World®

AR

# Single / Double Register Data Transfer

Use to move data between one or two registers and memory

| LDRD  | STRD | Doubleword           |                                      |                         |

|-------|------|----------------------|--------------------------------------|-------------------------|

| LDR   | STR  | Word                 |                                      |                         |

| LDRB  | STRB | Duto                 |                                      |                         |

| LDKD  | SIKD | Byte                 |                                      | Memory                  |

| LDRH  | STRH | Halfword             |                                      |                         |

| LDRSB |      | Signed byte load     |                                      |                         |

| LDRSH |      | Signed halfword load |                                      |                         |

|       |      |                      | 31                                   | $\sim$ 0                |

|       |      |                      | Rd Any remaining zero filled or sign | g space ←<br>n extended |

#### Syntax

- LDR{<size>}{<cond>} Rd, <address>

- STR{<size>}{<cond>} Rd, <address>

# Agenda

Introduction to ARM Ltd ARM Architecture/Programmers Model

Data Path and Pipelines

System Design

**Development Tools**

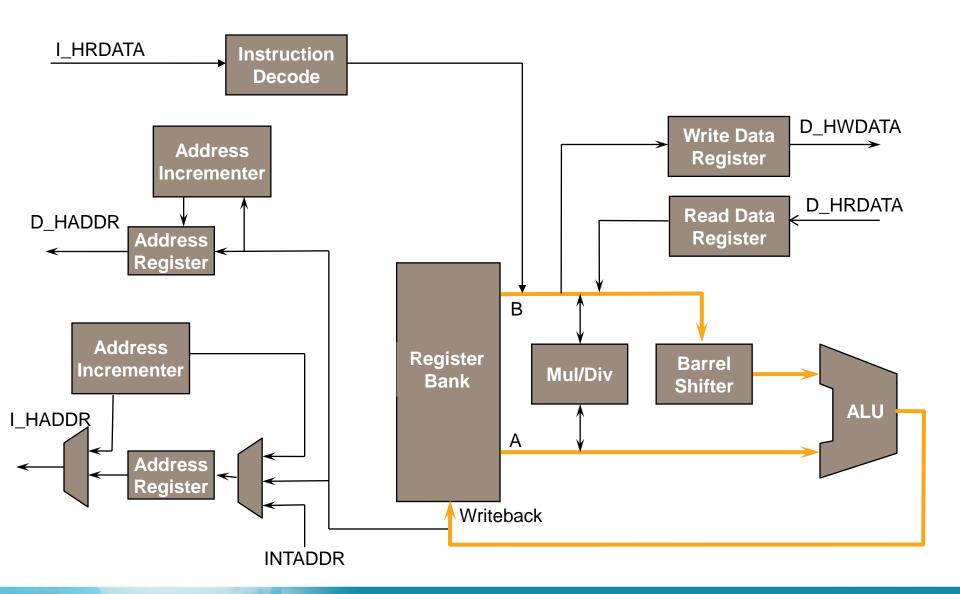

# **The ARM7TDM Core**

## **Cortex-M3 Datapath**

The Architecture for the Digital World®

ARM

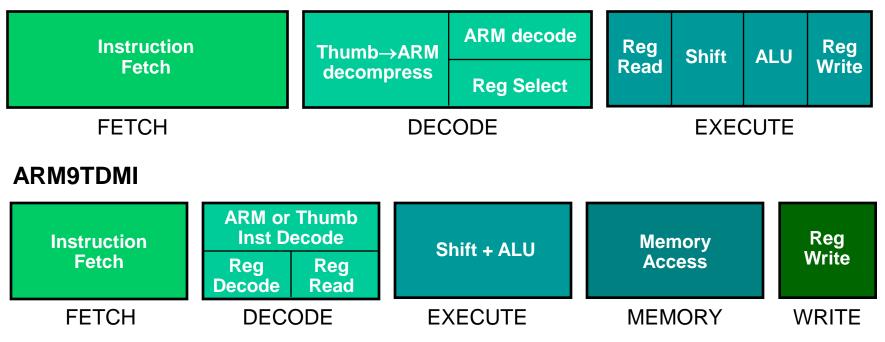

# **Pipeline changes for ARM9TDMI**

### **ARM7TDMI**

ARM

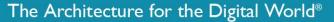

# **Cortex-M3 Pipeline**

- Cortex-M3 has 3-stage fetch-decode-execute pipeline

- Similar to ARM7

- Cortex-M3 does more in each stage to increase overall performance

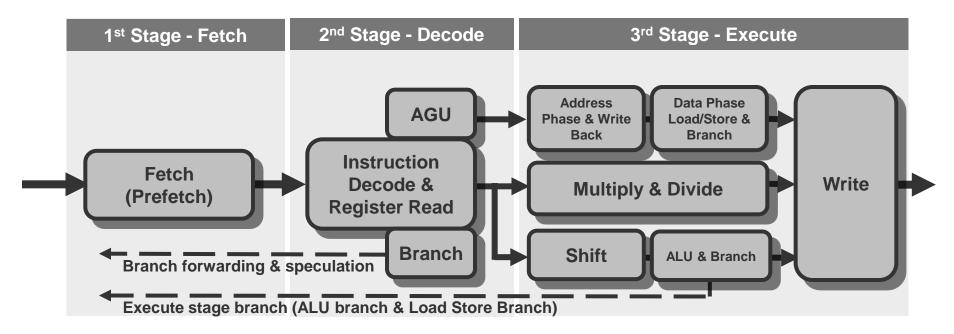

# **ARM10 vs. ARM11 Pipelines**

### ARM10

### ARM11

|            |            |        |       | Shift    | ALU                | Saturate           |               |

|------------|------------|--------|-------|----------|--------------------|--------------------|---------------|

| Fetch<br>1 | Fetch<br>2 | Decode | Issue | MAC<br>1 | MAC<br>2           | MAC<br>3           | Write<br>back |

|            |            |        |       | Address  | Data<br>Cache<br>1 | Data<br>Cache<br>2 |               |

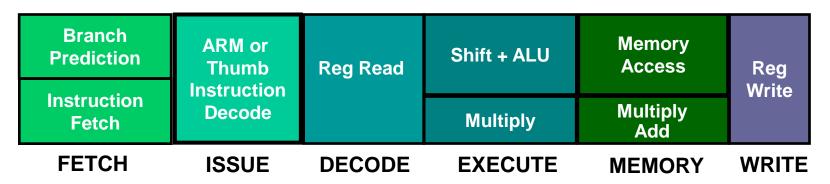

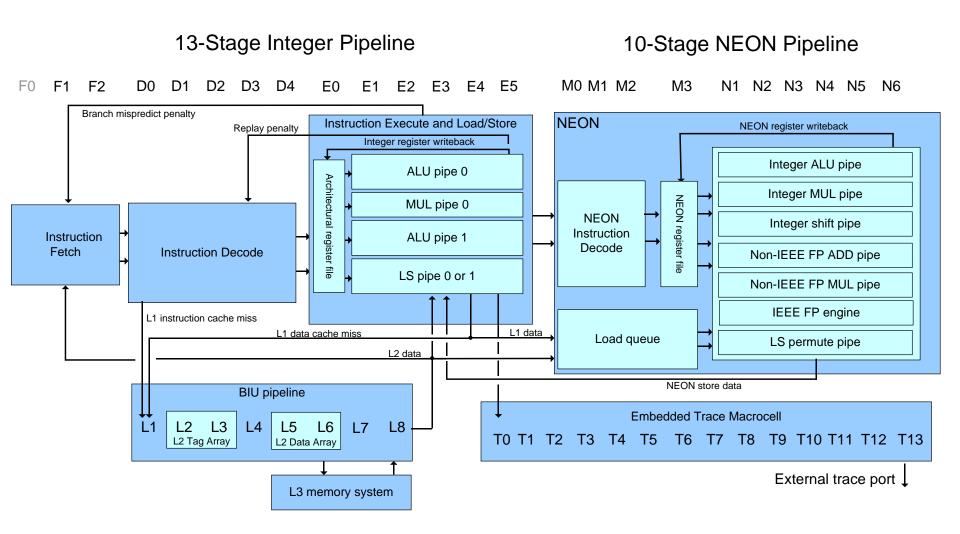

# **Full Cortex-A8 Pipeline Diagram**

# Agenda

Introduction to ARM Ltd

**ARM Architecture/Programmers Model**

**Data Path and Pipelines**

- System Design

- **Development Tools**

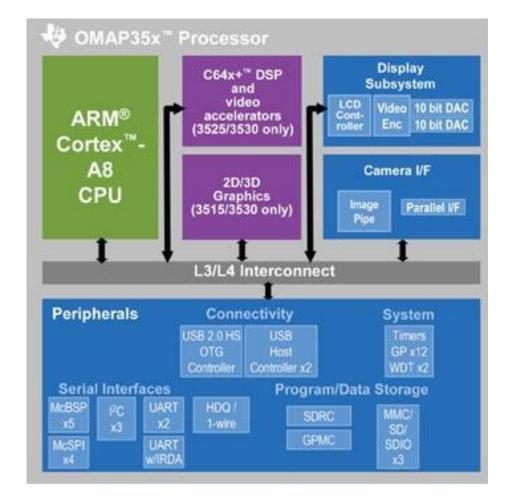

#### **TI OMAP35X SoC**

The Architecture for the Digital World®

ARM

### Agenda

Introduction to ARM Ltd ARM Architecture/Programmers Model Data Path and Pipelines System Design Development Tools

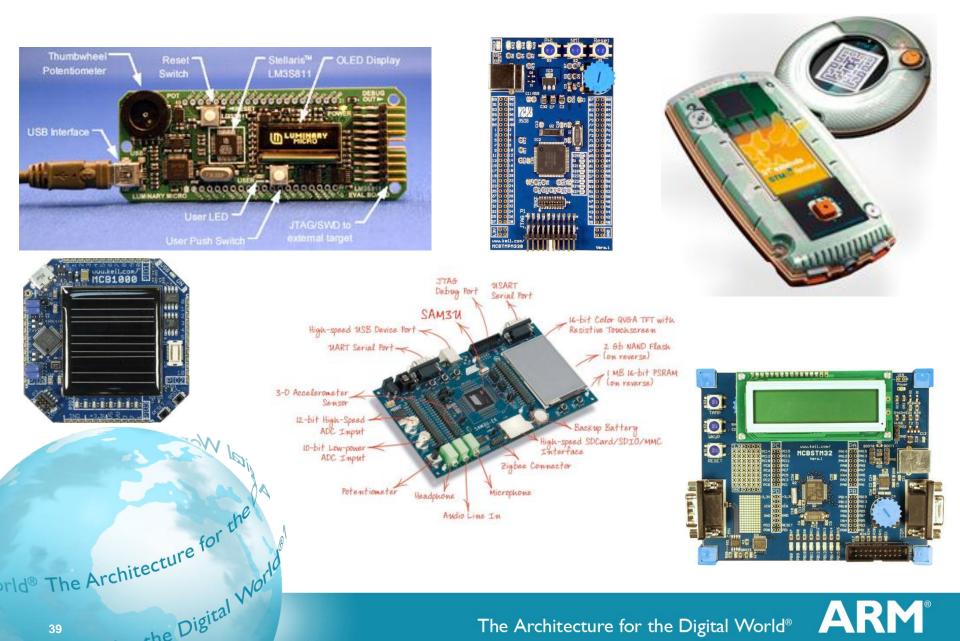

#### **Development Platforms**

### **Keil Development Tools for ARM**

- Includes ARM macro assembler, compilers (ARM RealView C/C++ Compiler, Keil CARM Compiler, or GNU compiler), ARM linker, Keil uVision Debugger and Keil uVision IDE

- Keil uVision Debugger accurately simulates on-chip peripherals (I<sup>2</sup>C, CAN, UART, SPI, Interrupts, I/O Ports, A/D and D/A converters, PWM, etc.)

- Evaluation Limitations

- 16K byte object code + 16K data limitation

- Some linker restrictions such as base addresses for code/constants

- GNU tools provided are not restricted in any way

- http://www.keil.com/demo/

#### **Keil Development Tools for ARM**

| ₩ Hello - µVision3 - [C:\Keil\ARM\E   | xamples\Hello\Hello.c]                                                             |          |

|---------------------------------------|------------------------------------------------------------------------------------|----------|

| 🖹 Eile Edit View Project Debug Fla    | ash Pe <u>ri</u> pherals <u>T</u> ools <u>S</u> VCS <u>W</u> indow <u>H</u> elp    | _ & ×    |

| -<br>[ 🎦 🍃 🔒 🍠 👗 🖻 🛍   으 오   1        | ≡ ∉ ∧ % % % ∰                                                                      |          |

| 1 않는 🗐 🐼 🖓 🖓 🖓 🖓 🔤 🕸                  | R 🖉 🌾 🕹 🗏 E 🚟 🖪 🔪                                                                  |          |

| ● 🕮 🎬 👗 🛱 🔊 LPC2100                   |                                                                                    |          |

| Project Workspace                     |                                                                                    |          |

| Register Value                        | 02 /* This file is part of the uVision/ARM development tools */                    | <b>_</b> |

| Current                               | 03 /* Copyright KEIL ELEKTRONIK GmbH 2002-2004 */                                  |          |

| R0 0x000000c                          |                                                                                    |          |

|                                       | 05 /* */ */ */ */ */ */ */                                                         |          |

| R2 0x00000020                         | 06 /* HELLO.C: Hello World Example */                                              |          |

| R4 0x00000000                         | 08 //***********************************                                           |          |

| R5 0x00000000                         | 09                                                                                 |          |

| R6 0x00000000                         | 10 #include <stdio.h> /* prototype declarations for I/O functions */</stdio.h>     |          |

| R7 0x00000000                         | 11     #include <lpc21xx.h>     /* LPC21xx definitions     */       12</lpc21xx.h> |          |

|                                       |                                                                                    |          |

| B10 0x00000000 V                      | 14 /***********                                                                    |          |

| 🖹 🗮 🔟 🐴 F 🗮 T                         | 15 /* main program */                                                              |          |

|                                       | 16 /************/<br>17 int main (void) { /* execution starts here */              |          |

| Symbols 🔺 🗙                           | 17 int main (void) {     /* execution starts here     */       18                  |          |

| M <u>a</u> sk: <b>*</b>               | 19 /* initialize the serial interface */                                           |          |

| Name Type 🔺                           | 20 PINSELO = 0x00050000; /* Enable RxD1 and TxD1 */                                |          |

|                                       | 21 U1LCR = 0x83; /* 8 bits, no Parity, 1 Stop bit */                               |          |

| E Sindado VIII Ed                     | 22 UIDLL = 97; /* 9600 Baud Rate @ 15MHz VPB Clock */                              |          |

| ALDOM uchar                           | 23 U1LCR = 0x03; /* DLAB = 0 */                                                    |          |

| →                                     | 27 printf ("Hello World\n"); /* the 'printf' function call */                      |          |

| ALDOY ushort                          | 26                                                                                 |          |

| → ALHOUR uchar<br>→ ALMIN uchar       | 27 while (1) { /* An embedded program does not stop and */                         |          |

| ALMON uchar                           |                                                                                    |          |

| ALSEC uchar 🔫                         | E Hello.c E Startup.s R Disassembly a Serial #2                                    |          |

| ▼ MISSING DEVICE (ROO3: SEC           | JRITY KEY NOT FOUND)                                                               | <b>_</b> |

| * Running in Eval Mode                |                                                                                    |          |

| Load "C:\\Keil\\ARM\\Exam]            |                                                                                    |          |

| *** Restricted Version with           |                                                                                    | 00 00    |

| *** Currently used: 1980 1            |                                                                                    | 0 00     |

| · · · · · · · · · · · · · · · · · · · |                                                                                    | 0 00     |

| Mundow                                |                                                                                    |          |

| ⊰<br>≒ ASSIGN BreakDisable Break      | Enable BreakKill BreakList 🖵 💈 0x0000404E: 00 00 00 00 00 00 00 00 00 00 00 00 00  |          |

| ASSIGN BreakDisable Break             |                                                                                    | <u> </u> |

| Ready                                 | Simulation t1: 0.72642057 sec L:29 C:1                                             |          |

| neauy                                 |                                                                                    |          |

#### **University Resources**

#### www.arm.com/university/

#### University@arm.com

# Your Future at ARM...

#### Graduate and Internship/Co-op Opportunities

- Engineering: Memory, Validation, Performance, DFT, R&D, GPU and more!

- Sales and Marketing: Corporate and Technical

- Corporate: IT, Patents, Services (Training and Support), and Human Resources

#### Incredible Culture and Comprehensive Benefit Package

- Competitive Reward

- Work/Life Balance

- Personal Development

- Brilliant Minds and Innovative Solutions

#### Keep in Touch!

www.arm.com/about/careers

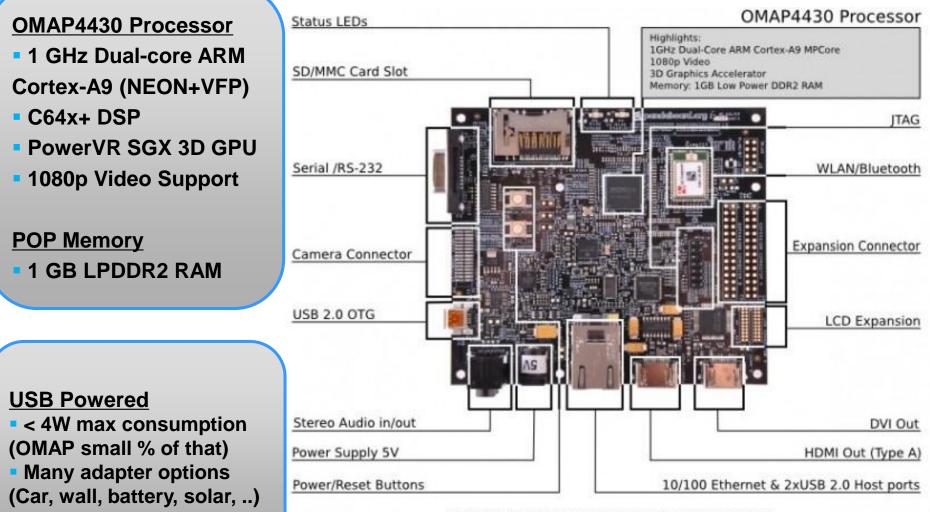

### **TI Panda Board**

Board Dimensions: W:4.0" (101.6 mm) X H: 4.5" (114.3 mm)

Id® The Architecture for the Joint Architecture

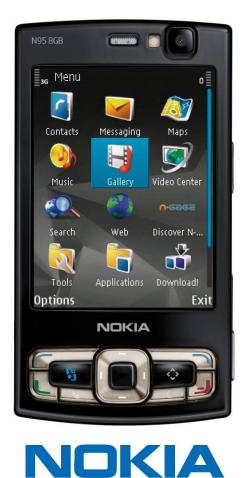

# Nokia N95 Multimedia Computer

# symbian

#### OMAP™ 2420

Applications Processor ARM1136<sup>™</sup> processor-based

SoC, developed using Magma ®

Blast® family and winner of 2005 INSIGHT Award for 'Most Innovative SoC'

Symbian OS<sup>™</sup> v9.2 Operating System supporting ARM processor-based mobile devices, developed using ARM® RealView® Compilation Tools

S60<sup>™</sup> 3<sup>rd</sup> Edition S60 Platform supporting ARM processor-based mobile devices

Mobiclip<sup>™</sup> Video Codec Software video codec for ARM processor-based mobile devices

ST WLAN Solution Ultra-low power 802.11b/g WLAN chip with ARM9<sup>™</sup> processor-based MAC

#### Connect. Collaborate. Create.

CONNECTING PEOPLE

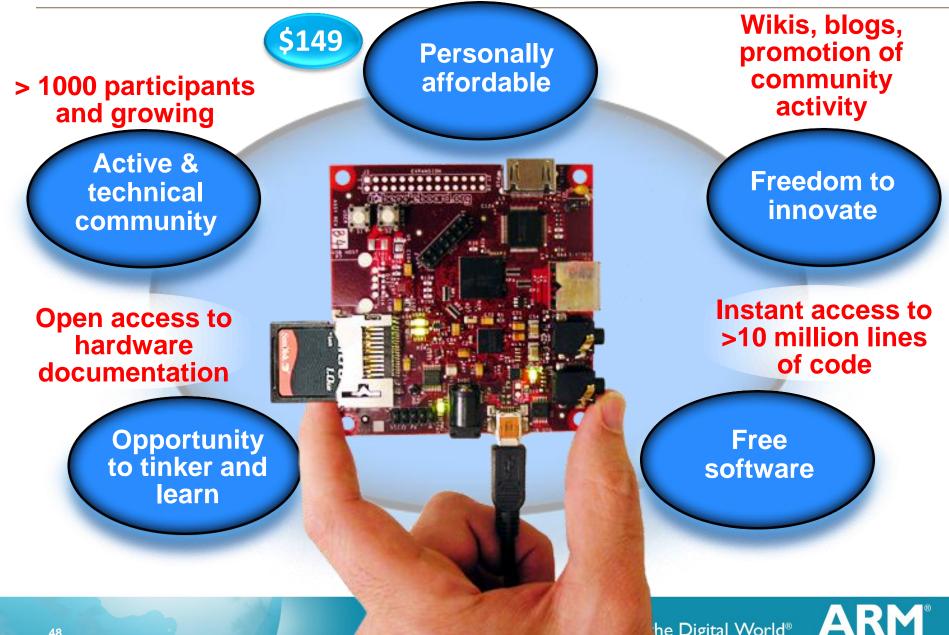

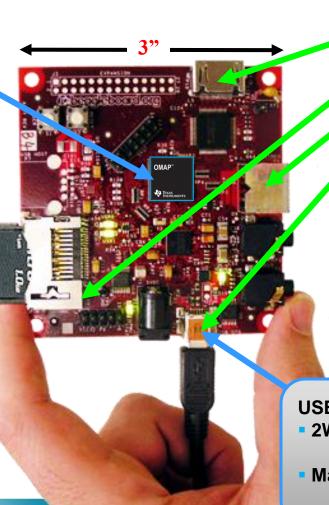

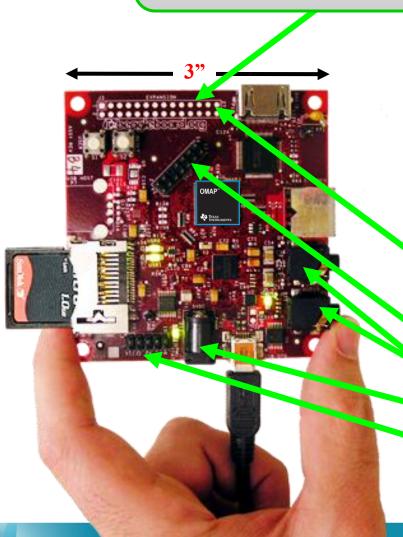

# **Beagle Board**

### **Targeting community development**

he Digital World®

### Fast, low power, flexible expansion

**OMAP3530** Processor 600MHz Cortex-A8 NEON+VFPv3 16KB/16KB L1\$ 256KB L2\$ 430MHz C64x+ DSP 32K/32K L1\$ • 48K L1D • 32K L2 PowerVR SGX GPU 64K on-chip RAM **POP Memory** 128MB LPDDR RAM 256MB NAND flash

49

DVI-D video out

SD/MMC+

S-Video out

USB 2.0 HS OTG

I<sup>2</sup>C, I<sup>2</sup>S, SPI,

**Peripheral I/O**

MMC/SD

- JTAG

- Stereo in/out

- Alternate power

- RS-232 serial

USB Powered

2W maximum consumption

OMAP is small % of that

Many adapter options

Car, wall, battery, solar, ...

he Digital World®

## And more...

On-going collaboration at **BeagleBoard.org**

- Live chat via IRC for 24/7 community support

- Links to software projects to download

- 4 LEDs

- USR0

- USR1

- PMU\_STAT

- PWR

- 2 buttons

- USER

- RESET

- 4 boot sources

- SD/MMC

- NAND flash

- USB

- Serial

Peripheral I/O

- DVI-D video out

- SD/MMC+

- S-Video out

- USB HS OTG

- I<sup>2</sup>C, I<sup>2</sup>S, SPI, MMC/SD

- JTAG

- Stereo in/out

- Alternate power

- **RS-232** serial

# **Project Ideas Using Beagle**

#### OS Projects

- OS porting to ARM/Cortex (TI OMAP)

- MythTV system

- "Super-Beagle" stack of Beagles as compute engine and task distribution

- Linux applications

#### NEON Optimization Projects

- Codec optimization in ffmpeg (pick your favorite codec)

- Voice and image recognition

- Open-source Flash player optimizations (swfdec)