## **Propagation Delays:**

Propagation delay (PD) for the circuit can be calculated as the summation of all delays encountered from where the clock occurs to the output.

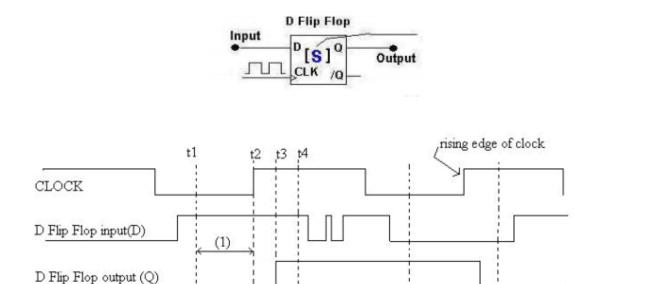

Propagation delay is the time required for the output to reach from 10% to 90% of its final output level when the input changes. Calculate from your wave forms. Example of a Data Flip-Flop shown below.

- (1) i.e. [t2 t1] is the Setup Time: the amount of time Input is held constant BEFORE the clock tick.

- (2) i.e. [t3 t2] is the Propagation delay of the Flip Flop: the time for the input to propagate and influence the output.

parameters are same for all Clock cycles

(3) i.e. [t4 - t2] is the Hold time: the amount of time the Input is held constant AFTER the clock tick.

(The above timing diagram has 2 clock cycles; the timing parameters for the second cycle will also be similar to that of the first cycle)

## Maximum clock rate:

Maximum clock rate is calculated using the formulae

So we will have to calculate TMIN first. TMIN here refers to the minimum time period for correct operation of the circuit, so it is calculated using all worst cases (maximum delays).

## Other useful things:

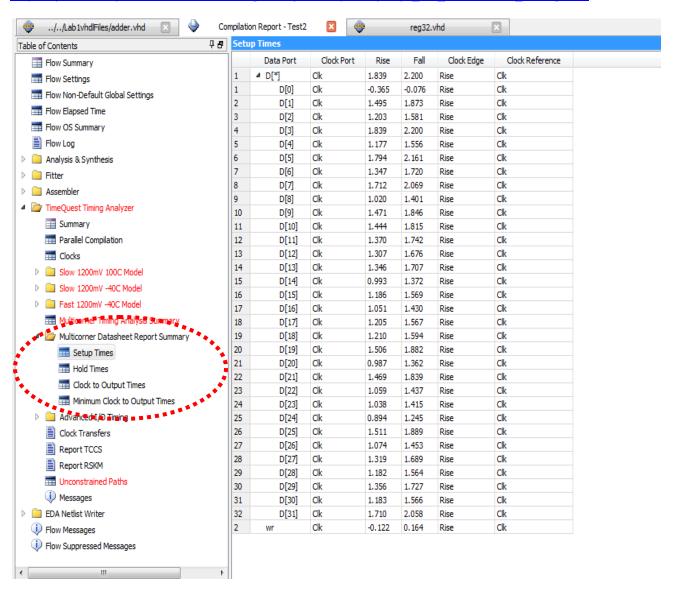

You can also calculate these delays using time quest multicorner timing and timing model datasheet reports.

Following link shows description of what each report shows plus what each row/column in the report signifies

http://quartushelp.altera.com/13.0/mergedProjects/report/rpt/rpt file multicorner timing.htm