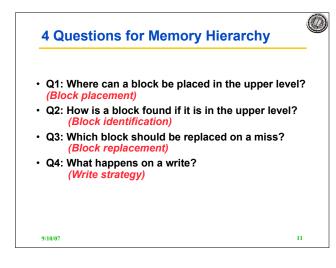

## Q3: Which block should be replaced on a miss?

- · Easy for Direct Mapped

- · Set Associative or Fully Associative:

- Random

- LRU (Least Recently Used)

8-way 2-way Assoc: 4-way LRU Size LRU Ran LRU Ran Ran 5.2% 5.7% 4.7% 5.3% 4.4% 5.0% 64 KB 1.9% 2.0% 1.5% 1.7% 1.4% 1.5% 256 KB 1.15% 1.17% 1.13% 1.13% 1.12% 1.12%

9/10/07

## **5 Basic Cache Optimizations**

17

- Reducing Miss Rate

- 1. Larger Block size (compulsory misses)

- 2. Larger Cache size (capacity misses)

- 3. Higher Associativity (conflict misses)

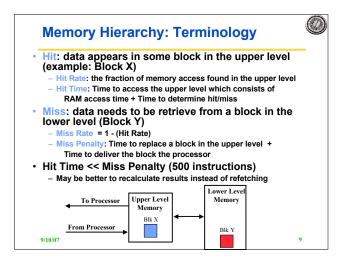

- · Reducing Miss Penalty

- 4. Multilevel Caches

- · Reducing hit time

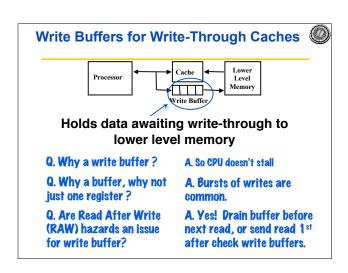

- 5. Giving Reads Priority over Writes

- · E.g., Read complete before earlier writes in write buffer

9/10/07

## Outline

18

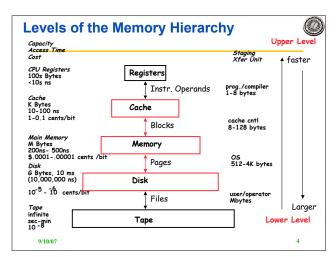

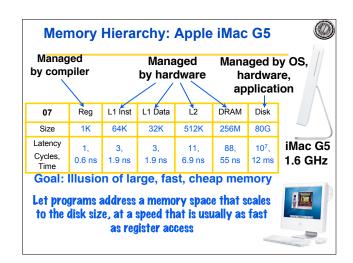

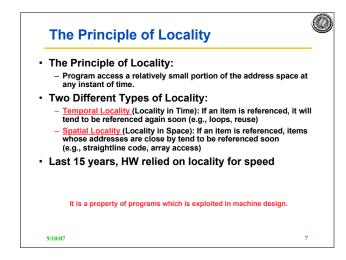

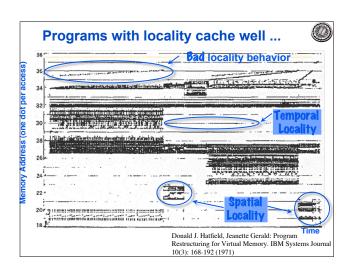

- · Memory hierarchy

- Locality

- Cache design

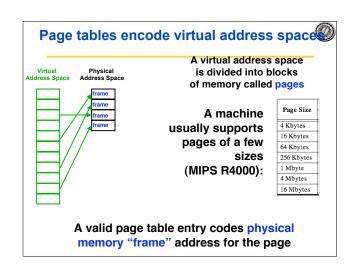

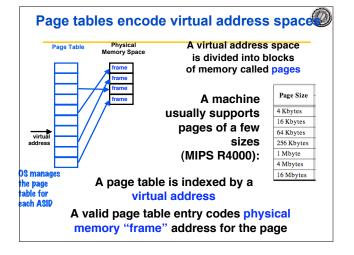

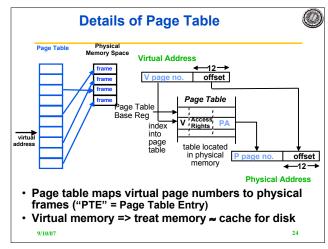

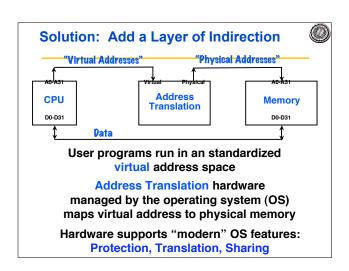

- Virtual address spaces

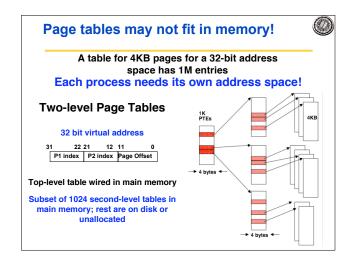

- · Page table layout

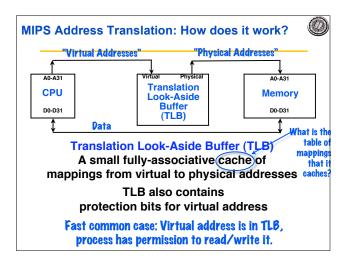

- TLB design options

9/10/07

## The Limits of Physical Addressing "Physical addresses" of memory locations A0-A31 CPU D0-D31 Data All programs share one address space: The physical address space Machine language programs must be aware of the machine organization No way to prevent a program from accessing any machine resource

CS252 S05 5