These slides are provided by: David Patterson Electrical Engineering and Computer Sciences, University of California, Berkeley Modifications/additions have been made from the originals

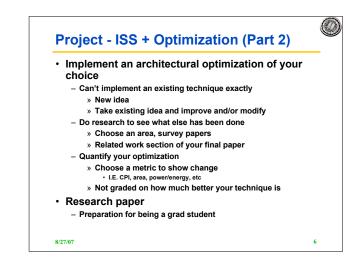

- · ISS for your own custom assembly language

- Reads in program in intermediate format

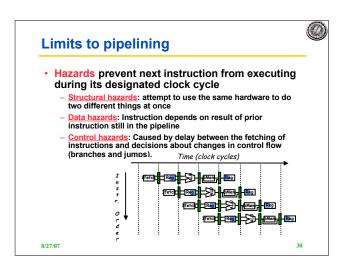

- Pipelined (5 stage) and cycle accurate

- Must deal with data and control hazards

- Must implement any potential pipeline forwarding and resource sharing (register file) to minimize stall cycles

- Outputs any computed values in registers or memory to verify functionality

#### Assembler

- Input = assembly code

- Output = intermediate format (opcodes and addresses)

- Testing

- You will need to write applications

- Matrix multiple, GCD, etc

8/27/07

5

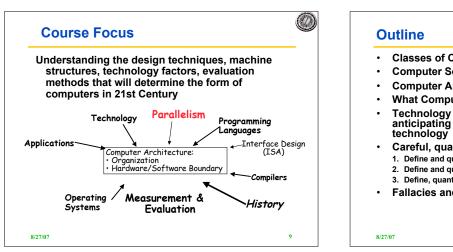

| <ul> <li>Classes of Computers</li> <li>Computer Science at a Crossroads</li> <li>Computer Architecture v. Instruction Set Arch.</li> <li>What Computer Architecture brings to table</li> <li>Technology Trends: Culture of tracking,<br/>anticipating and exploiting advances in<br/>technology</li> </ul> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Careful, quantitative comparisons:         <ol> <li>Define and quantity power</li> <li>Define and quantity dependability</li> <li>Define, quantity, and summarize relative performance</li> </ol> </li> <li>Fallacies and Pitfalls</li> </ul>                                                     |

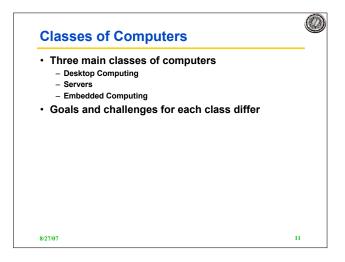

|          | Price of<br>system      | Price of<br>micro-<br>processor<br>module | Critical system design issues                                    |  |  |

|----------|-------------------------|-------------------------------------------|------------------------------------------------------------------|--|--|

| Desktop  | \$500-<br>\$5,000       | \$50-\$500                                | Price-performance     Graphics performance                       |  |  |

| Server   | \$5,000-<br>\$5,000,000 | \$200-<br>\$10,000                        | •Throughput<br>•Availability/Dependability<br>•Scalability       |  |  |

| Embedded | \$10-<br>\$100,000      | \$0.01-<br>\$100                          | Price     Power consumption     Application-specific performance |  |  |

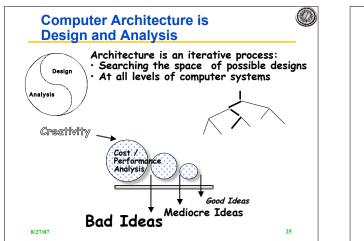

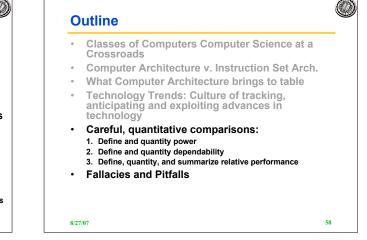

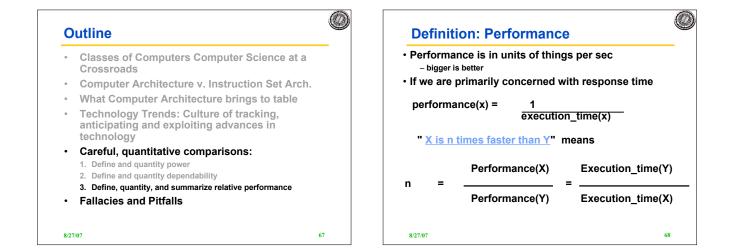

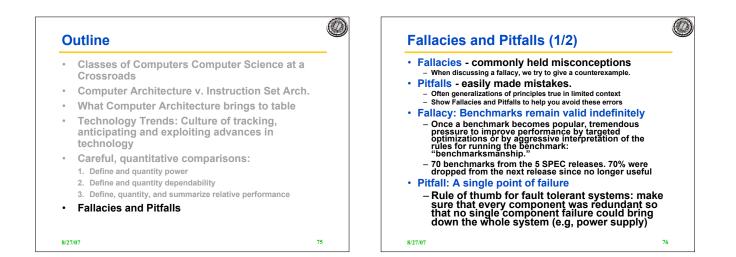

#### **Outline**

- Classes of Computers

- Computer Science at a Crossroads

- Computer Architecture v. Instruction Set Arch.

- · What Computer Architecture brings to table

- Technology Trends: Culture of tracking, anticipating and exploiting advances in technology

- Careful, quantitative comparisons:

- 1. Define and quantity power

- 2. Define and quantity dependability

- 3. Define, quantity, and summarize relative performance

- · Fallacies and Pitfalls

8/27/07

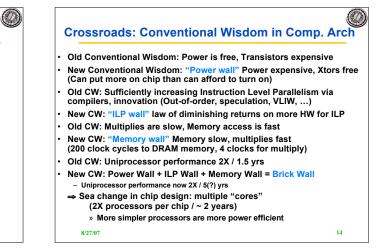

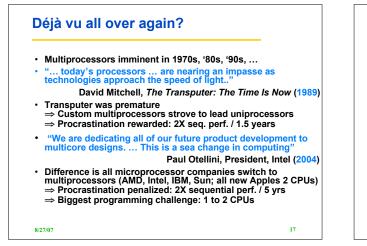

# **Problems with Sea Change**

8/27/07

Algorithms, Programming Languages, Compilers, Operating Systems, Architectures, Libraries, ... not ready to supply Thread Level Parallelism or Data Level Parallelism for 1000 CPUs / chip,

18

- Architectures not ready for 1000 CPUs / chip Unlike Instruction Level Parallelism, cannot be solved by just by computer architects and compiler writers alone, but also cannot be solved *without* participation of computer architects

- Computer Architecture: A Quantitative Approach) explores shift from Instruction Level Parallelism to Thread Level Parallelism / Data Level Parallelism

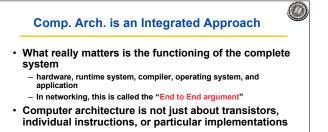

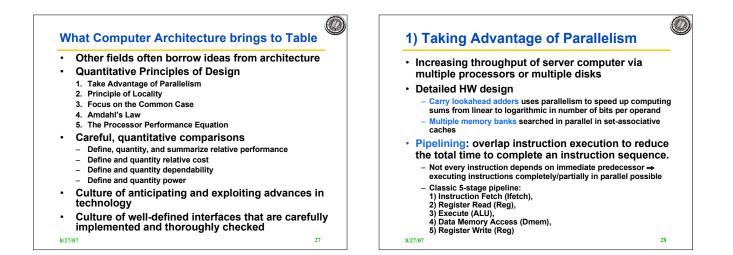

Outline **Classes of Computers Computer Science at a Crossroads** software Computer Architecture v. Instruction Set Arch. What Computer Architecture brings to table Technology Trends: Culture of tracking, anticipating and exploiting advances in technology hardware Careful, quantitative comparisons: 1. Define and quantity power 2. Define and quantity dependability 3. Define, quantity, and summarize relative performance Fallacies and Pitfalls 8/27/07 19 8/27/07

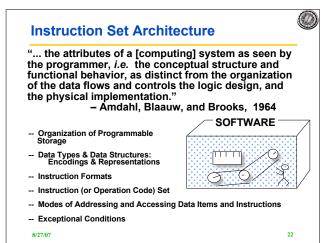

Instruction Set Architecture: Critical Interface instruction set · Properties of a good abstraction Lasts through many generations (portability) - Used in many different ways (generality) - Provides convenient functionality to higher levels - Permits an efficient implementation at lower levels 20

| I. | SA vs. Computer Architecture                                                                                                                                          |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •  | Old definition of computer architecture<br>= instruction set design                                                                                                   |

|    | <ul> <li>Other aspects of computer design called implementation</li> <li>Insinuates implementation is uninteresting or less challenging</li> </ul>                    |

| •  | Our view is computer architecture >> ISA                                                                                                                              |

| •  | Architect's job much more than instruction set design; technical hurdles today <i>more</i> challenging than those in instruction set design                           |

| •  | Since instruction set design not where action is,<br>some conclude computer architecture (using old<br>definition) is not where action is<br>– Disagree on conclusion |

|    | <ul> <li>Agree that ISA not where action is (ISA in CA:AQA 4/e appendix</li> </ul>                                                                                    |

8/27/07

23

### CS252 S05

|                          |            |               | inst count Cycle                      |

|--------------------------|------------|---------------|---------------------------------------|

| CPU time = Seco<br>Progr |            | tions x<br>am | Cycles x Seconds<br>Instruction Cycle |

|                          | Inst Count | CPI           | Clock Rate                            |

| Program                  | х          |               |                                       |

| Compiler                 | x          | (X)           |                                       |

| Inst. Set.               | х          | х             |                                       |

| Organization             |            | X             | X                                     |

| Technology               |            |               | x                                     |

(D)

## CS252 S05

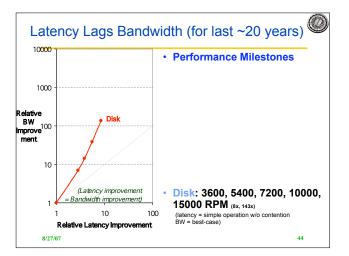

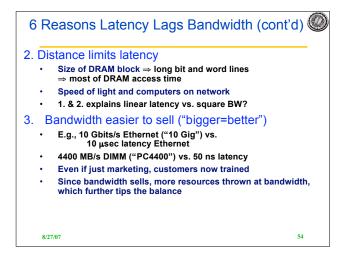

| <ul> <li>CDC Wren I, 1983</li> </ul>              | • | Seagate 373453, 200                      | )3      |

|---------------------------------------------------|---|------------------------------------------|---------|

| • 3600 RPM                                        | • | 15000 RPM                                | (4X)    |

| 0.03 GBytes capacity                              | • | 73.4 GBytes                              | (2500X) |

| Tracks/Inch: 800                                  | • | Tracks/Inch: 64000                       | (80X    |

| Bits/Inch: 9550                                   | • | Bits/Inch: 533,000                       | (60X    |

| Three 5.25" platters                              | • | Four 2.5" platters (in 3.5" form factor) |         |

| <ul> <li>Bandwidth:<br/>0.6 MBytes/sec</li> </ul> | • | Bandwidth:<br>86 MBytes/sec              | (140X)  |

| Latency: 48.3 ms                                  | • | Latency: 5.7 ms                          | (8X)    |

| Cache: none                                       | • | Cache: 8 MBytes                          |         |

#### CS252 S05

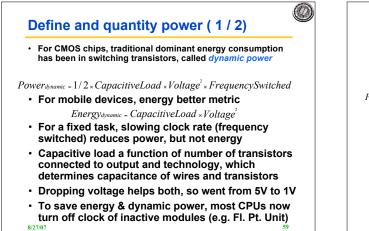

Because leakage current flows even when a transistor is off, now *static power* important too

Powerstatic - Currentstatic × Voltage

- · Leakage current increases in processors with smaller transistor sizes

- · Increasing the number of transistors increases power even if they are turned off

- · In 2006, goal for leakage is 25% of total power consumption; high performance designs at 40%

- Very low power systems even gate voltage to inactive modules to control loss due to leakage

8/27/07

61

63

(D)

# Outline

- **Classes of Computers Computer Science at a** Crossroads

- Computer Architecture v. Instruction Set Arch.

- What Computer Architecture brings to table

- Technology Trends: Culture of tracking. anticipating and exploiting advances in technology

- Careful, quantitative comparisons:

- Define and quantity power

- 2. Define and quantity dependability

- 3. Define, quantity, and summarize relative performance **Fallacies and Pitfalls**

62

8/27/07

Define and quantity dependability (1/3) How decide when a system is operating properly? Infrastructure providers now offer Service Level Agreements (SLA) to guarantee that their networking or power service would be dependable Systems alternate between 2 states of service with respect to an SLA: Service accomplishment, where the service is 1. delivered as specified in SLA Service interruption, where the delivered service is different from the SLA 2 Failure = transition from state 1 to state 2 Restoration = transition from state 2 to state 1

8/27/07

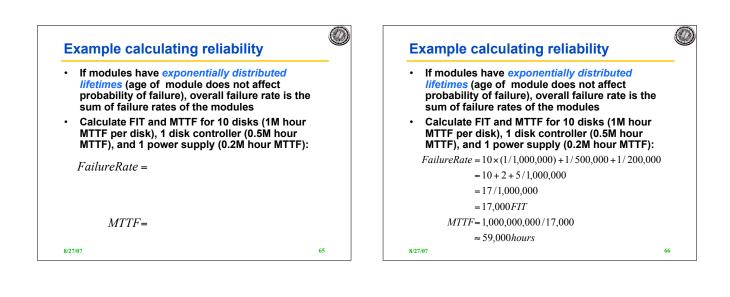

Define and quantity dependability (2/3) Module reliability = measure of continuous service accomplishment (or time to failure). 2 metrics 1. Mean Time To Failure (MTTF) measures Reliability 2. Failures In Time (FIT) = 1/MTTF, the rate of failures Traditionally reported as failures per billion hours of operation Mean Time To Repair (MTTR) measures Service Interruption Mean Time Between Failures (MTBF) = MTTF+MTTR Module availability measures service as alternate between the 2 states of accomplishment and interruption (number between 0 and 1, e.g. 0.9) Module availability = MTTF / (MTTF + MTTR) • 8/27/07 64

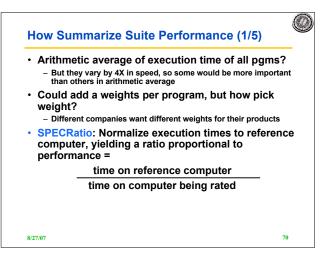

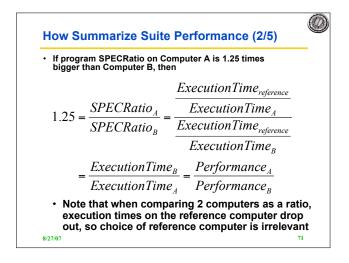

- · Usually rely on benchmarks vs. real workloads

- To increase predictability, collections of benchmark applications, called *benchmark suites*, are popular

(D)

- SPECCPU: popular desktop benchmark suite

- CPU only, split between integer and floating point programs

- SPECint2000 has 12 integer, SPECfp2000 has 14 integer pgms

- SPECCPU2006 to be announced Spring 2006

- SPECSFS (NFS file server) and SPECWeb (WebServer) added as server benchmarks

- Transaction Processing Council measures server performance and cost-performance for databases

- TPC-C Complex query for Online Transaction Processing

- TPC-H models ad hoc decision support

- TPC-W a transactional web benchmark

- TPC-App application server and web services benchmark

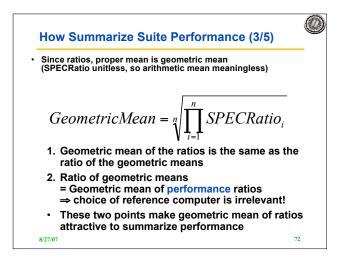

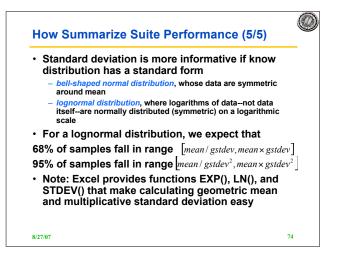

- Does a single mean well summarize performance of programs in benchmark suite?

- Can decide if mean a good predictor by characterizing variability of distribution using standard deviation

- Like geometric mean, geometric standard deviation is multiplicative rather than arithmetic

- Can simply take the logarithm of SPECRatios, compute the standard mean and standard deviation, and then take the exponent to convert back:

$GeometricMean = \exp\left(\frac{1}{n} \times \sum_{i=1}^{n} \ln(SPECRatio_i)\right)$

$GeometricStDev = \exp(StDev(\ln(SPECRatio_i))))$

8/27/07

73

Fallacy - Rated MTTF of disks is 1,200,000 hours or ~ 140 years, so disks practically never fail

- But disk lifetime is 5 years ⇒ replace a disk every 5 years; on average, 28 replacements wouldn't fail

- A better unit: % that fail (1.2M MTTF = 833 FIT)

- Fail over lifetime: if had 1000 disks for 5 years

= 1000\*(5\*365\*24)\*833 /10<sup>9</sup> = 36,485,000 / 10<sup>6</sup> = 37

= 3.7% (37/1000) fail over 5 yr lifetime (1.2M hr MTTF)

- But this is under pristine conditions – little vibration, narrow temperature range ⇒ no power failures

- Real world: 3% to 6% of SCSI drives fail per year

3400 6800 FIT or 150,000 300,000 hour MTTF [Gray & van Ingen 05]