### **EEL 5764: Graduate Computer Architecture**

## **Appendix A - Pipelining Review**

Ann Gordon-Ross Electrical and Computer Engineering University of Florida

http://www.ann.ece.ufl.edu/

These slides are provided by: David Patterson

David Patterson

Electrical Engineering and Computer Sciences, University of California, Berkeley

Modifications/additions have been made from the originals

## What is Pipelining?

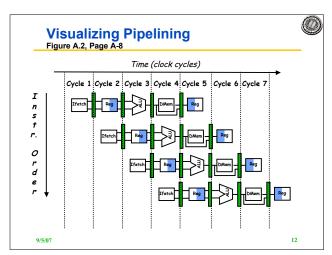

- · Overlapping execution to produce faster results

- Washing and drying dishes

- Washing and drying laundry

- Automobile assembly line

- Chipotle, Quiznos, etc

- · Pipelining in computer architecture

- Multiple instructions are overlapped in execution

- Exploits parallelism

- Not visible to programmer

- · Each stage is a pipeline "cycle"

- Each stage happens simultaneously so results are produced only as fast as the longest pipeline cycle

- Determines clock cycle time

9/5/07

2

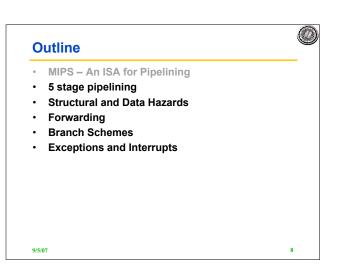

#### **Outline**

- MIPS An ISA for Pipelining

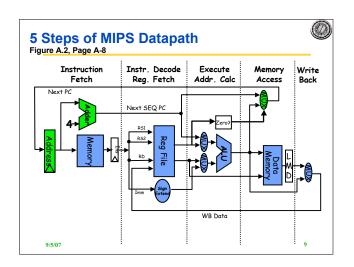

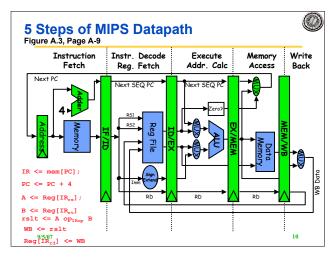

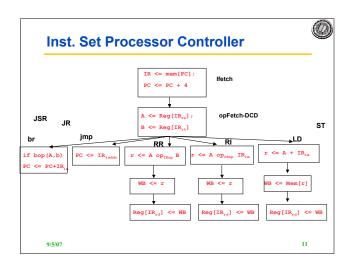

- 5 stage pipelining

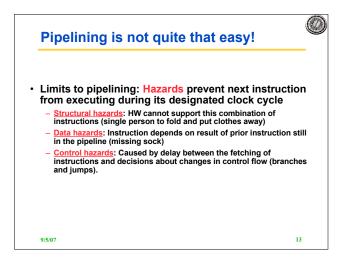

- Structural and Data Hazards

- Forwarding

- Branch Schemes

- Exceptions and Interrupts

# A "Typical" RISC ISA (Load/Store)

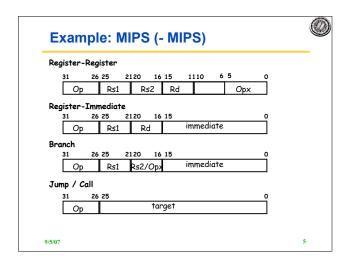

- 32-bit fixed format instruction (3 formats)

- 32 32-bit GPR (R0 contains zero)

- ALU instructions

- 3-address, reg-reg arithmetic instruction

- 2-address, reg-im arithmetic instruction

- Single address mode for load/store: base + displacement

- no indirection

- · Simple branch conditions

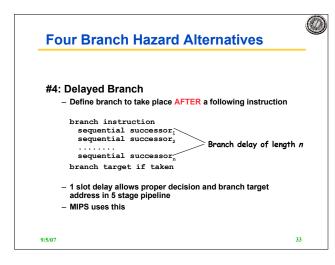

- Delayed branch

9/5/07

4

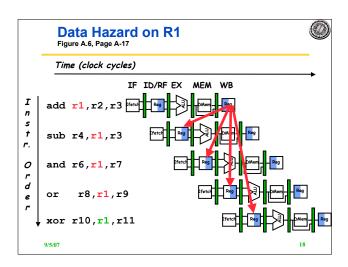

## **Three Generic Data Hazards**

19

17

Read After Write (RAW) Instr<sub>J</sub> tries to read operand before Instr<sub>I</sub> writes it

Caused by a "Dependence" (in compiler nomenclature). This hazard results from an actual need for communication.

/5/07

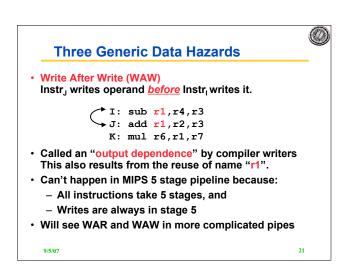

#### **Three Generic Data Hazards**

20

Write After Read (WAR)

Instr, writes operand <u>before</u> Instr, reads it

I: sub r4,r1,r3

J: add r1,r2,r3

K: mul r6,r1,r7

- Called an "anti-dependence" by compiler writers. This results from reuse of the name "r1".

- · Can't happen in MIPS 5 stage pipeline because:

- All instructions take 5 stages, and

- Reads are always in stage 2, and

- Writes are always in stage 5

• •

CS252 S05 5