## MULTI-PROCESSOR EMBEDDED Systems

Ann Melnichuk Long Talk

#### REFERENCE

Multi-Core Embedded Systems Edited by Georgios Kornaros CRC Press 2010Pages 1–29 Print ISBN: 978-1-4398-1161-0 eBook ISBN: 978-1-4398-1162-7 DOI: 10.1201/9781439811627-c1 http://www.crcnetbase.com/doi/book/10.1201/97814 39811627

#### DEFINITIONS

#### System-on-Chip (SoC)

multiple processors local DRAM flash memory hardware accelerators RF components

#### Network-on-Chip (NoC)

communication subsystem between IP cores in a System-on-a-Chip (SoC)

## **OVERVIEW OF THE BOOK**

#### Multi-Core Architecture for Embedded Systems

- Overview of the various multi-core architectures

- Discussion about the challenges

- Will be the focus of this presentation

#### Application-Specific Customizable Embedded Systems

- discussion about customizable processors in the context of MPSoC

- For a given embedded application:

- special instructions

- special functional units

- custom data widths

- custom register file structure

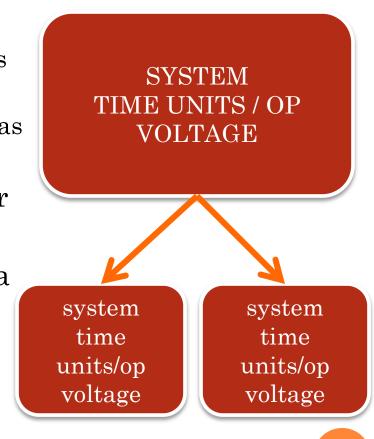

#### Power Optimizations in MCSoC

• Power analysis tools

#### Low power design

- Dynamic power management (DPM)

- Dynamic voltage scaling (DVS)

|   | Power Management<br>Methods | Pros                                                                                                | Cons                                                                         |  |

|---|-----------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|

|   | Clock Gating                | Simple additional gating logic                                                                      | Leakage power<br>dissipation<br>Medium power/<br>ground noise                |  |

|   | Power Gating                | No leakage                                                                                          | Complex additional<br>p/g switching logic<br>High power/ground<br>noise      |  |

|   | DVFS                        | Good controllability<br>between power and<br>performance<br>Low p/g noise                           | Complex additional<br>on-chip p/g voltage<br>regulators required             |  |

|   | Smart Caching               | Software controlled<br>Some level of optimization<br>possible between power<br>and performance      | Cache logic increases<br>Verification of<br>coherence protocols<br>difficult |  |

| ) | Scheduling                  | Global power optimization<br>possibly unlike all other<br>methods<br>Good control over p/g<br>noise | Kernel or user code<br>has to be changed                                     |  |

#### Routing Algorithms for Irregular Mesh-Based NoC

- O 2D mesh NoC built with different types of cores

→ thus irregular

- Various routing models

- Presentation and explanation of several algorithms

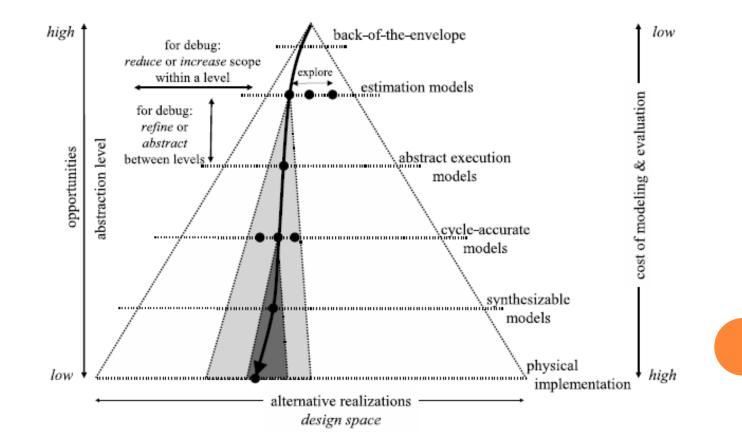

## Debugging Multi-Core Systems-on-ChipHigher level of abstraction

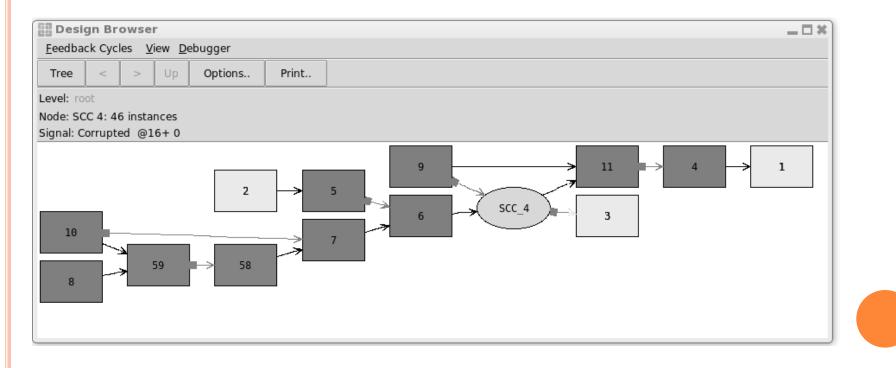

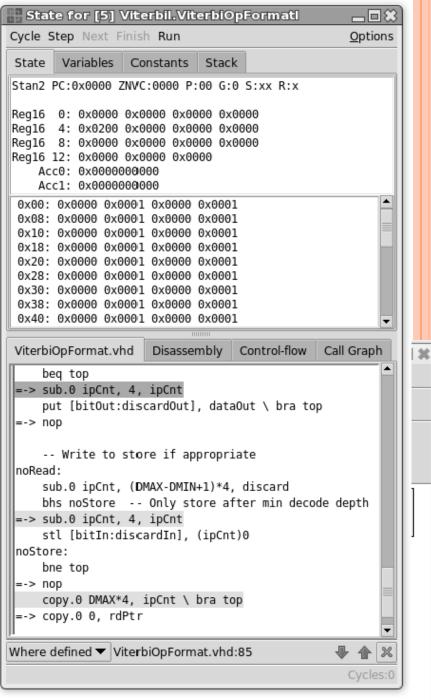

#### **Debugging Multi-Core Systems-on-Chip**

#### • Debugging tool which allows one to "zoom in" on the error

## **Debugging Multi-Core Syst**

#### • Debugging tool which allows the error

| 🔠 Design Browser                                      |           |       |             |  |  |  |  |  |  |  |  |

|-------------------------------------------------------|-----------|-------|-------------|--|--|--|--|--|--|--|--|

| <u>F</u> eedback Cycles <u>V</u> iew <u>D</u> ebugger |           |       |             |  |  |  |  |  |  |  |  |

| Tree < > U                                            | Options   | Print |             |  |  |  |  |  |  |  |  |

| Level: root                                           |           |       |             |  |  |  |  |  |  |  |  |

| Node: SCC 4: 46 instances<br>Signal: Corrupted @16+   |           |       |             |  |  |  |  |  |  |  |  |

| 10<br>59<br>8                                         | 2<br>→ 58 |       | 9<br>5<br>7 |  |  |  |  |  |  |  |  |

#### System-Level Tools for NoC-Based Multi-Core Design

- Theoretical discussion on network topology for NoC

- General graph theory with applications

- Borrowing from other fields: traffic modeling, network simulation, etc.

- SCOTCH tool examples

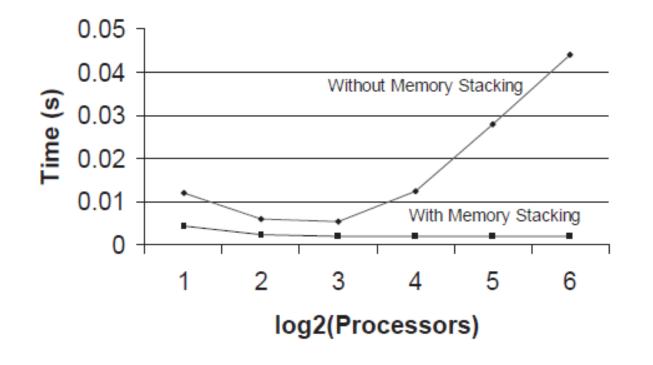

#### Compiler Techniques for Application Level Memory Optimization for MPSoC

- General memory optimization techniques

- Loop transformations

- Partitioning

#### Programming Models for Multi-Core Embedded Software

- Shared memory models: OpenMP

- Distributed memory models: MPI

- Languages designed for parallelism: CUDA, Estral, LUSTRE, SIGNAL (with examples)

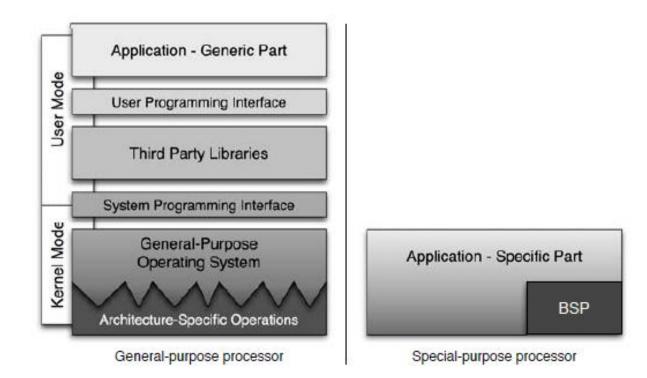

### **Operating System Support for MCSoC**

- Industrial and domain-specific software

- Designing the operating system

#### Autonomous Power Management in Embedded Multi-Cores

- More important for embedded multi-cores then the regular CPUs

- CASPER top-down integrated simulation for MC systems

#### **MCSoC** in Real World Products

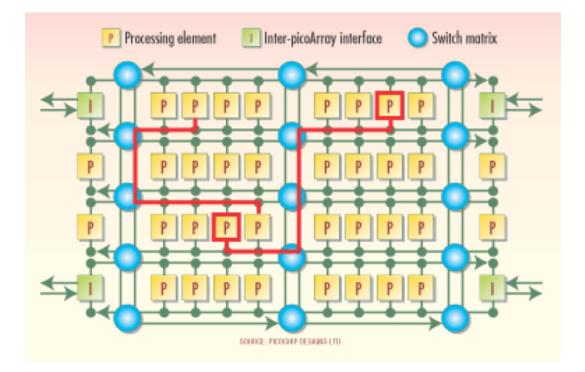

- Details about the picoChip and the picoArray

- Tiled architecture (100s processors)

#### Embedded Multi-Core Processing for Networking

- Network processing units (NPU)

- Fully programmable like DSPs

- Optimized for transmitting packets and cells

# WHAT MAKES MP SOLUTIONS ATTRACTIVE?

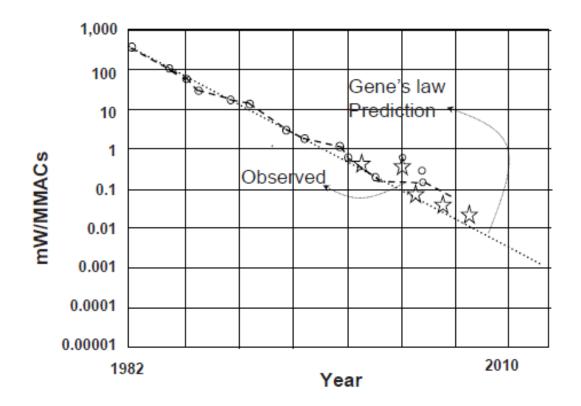

#### • Power Dissipation

• Hardware Implementation

## POWER DISSIPATION IN ES CONTEXT

## • Power dissipation of hand-held devices needs to be controlled. Or else...

## MP POWER DISSIPATION ADVANTAGES

#### • multiple power domains

- sub-systems may be turned on/off as dictated by usage

- I/O interfaces may be turned on/off as needed

- **gated clocking** clock system for a sub-system can be turned off

- **power gating** power supply to a sub-system can be turned off

## MP POWER DISSIPATION ADVANTAGES

#### • multiple power domains

- sub-systems may be turned on/off as dictated by usage

- I/O interfaces may be turned on/off as needed

- **gated clocking** clock system for a sub-system can be turned off

- **power gating** power supply to a sub-system can be turned off

- getting the same number of operations/s with less power

#### HARDWARE IMPLEMENTATION

Automated logic design is more efficiently done with small multiple processors rather than single high freq CPUs

- **Timing-closure** problem at high clock speeds

- Resistance

- Capacitance

- Inductance

- Difficult to predict the **critical paths**

## HARDWARE IMPLEMENTATION

#### o Divide-and-conquer

- design smaller blocks

- reuse templates

- control on-chip temperature variability

- more efficient testing patterns

- *Replication is your friend*

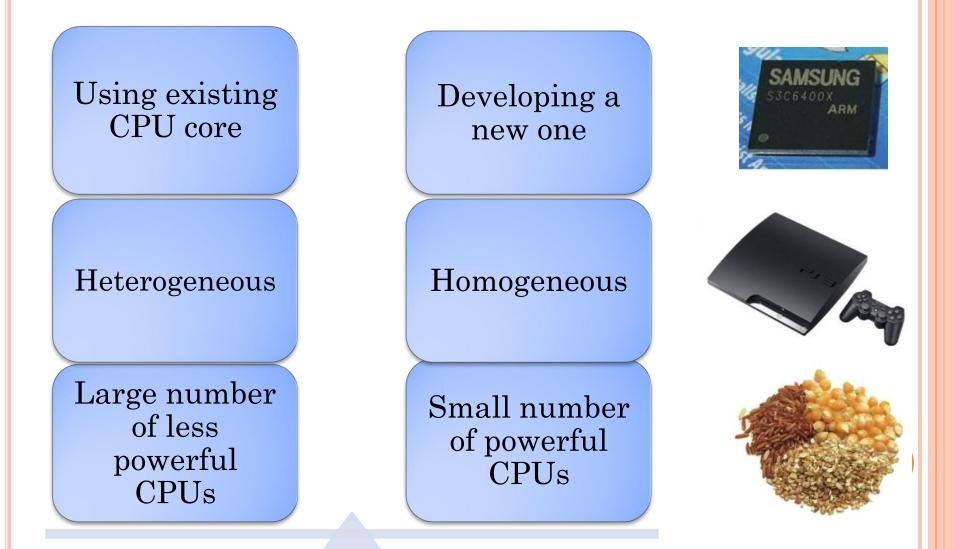

## ARCHITECTURAL DESIGN DECISIONS

### MEMORY CONSIDERATIONS

#### • Memory limitations

• Memory management is the main limiting factor in the performance of parallel machines

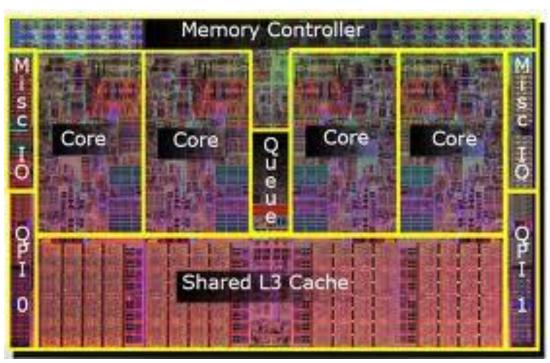

## MEMORY CONSIDERATIONS

- Memory occupies more than 50% of the die area in modern MPSoCs

- Variations:

- Distributed shared

- Centrally shared

- Not shared

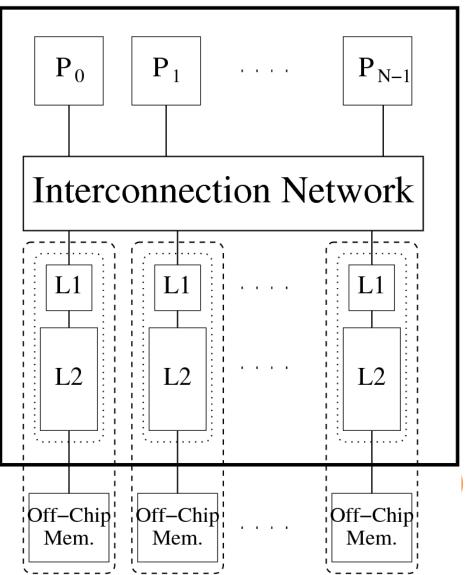

## **INTERCONNECTION NETWORKS**

### • Major considerations:

- Propagation delay

- Testabilty

- Layout area

- Expandability

#### **INTERCONNECTION NETWORKS**

- While the busses are the most popular scheme today, they do no scale well

- A modular approach is needed

http://www.csl.cornell.edu/courses/ece5970/

```

NETWORK-ON-CHIP (NOC)

```

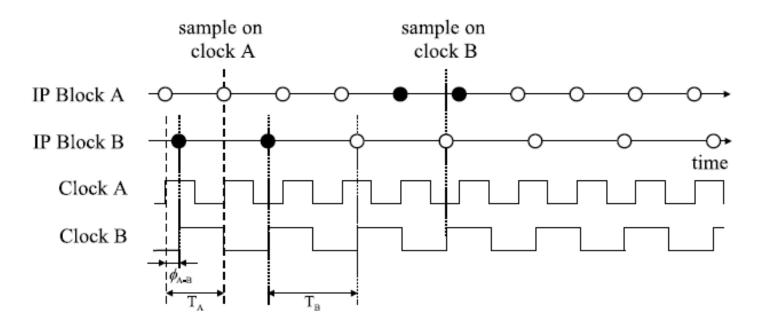

## • Globally Asynchronous, Locally Synchronous (GALS)

FIGURE 5.3: Lack of consistent global state with multiple, asynchronous clocks.

```

NETWORK-ON-CHIP (NOC)

```

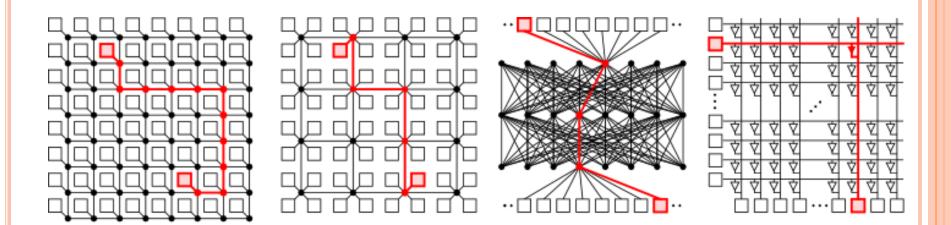

- Globally Asynchronous, Locally Synchronous (GALS)

- Possible Architectures:

- 2D mesh

- Tree based architecture

- Irregular

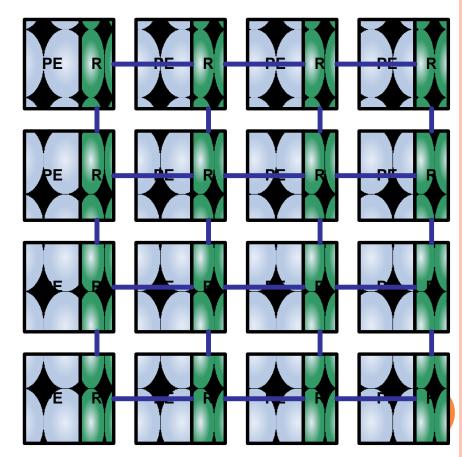

### 2D MESH TOPOLOGY

#### Regular 2D Mesh

R R R D PE PE PÈ R R Ř R PE PE PE R R PE PE PE

#### Tiled 2D Mesh

Eyal Friedman

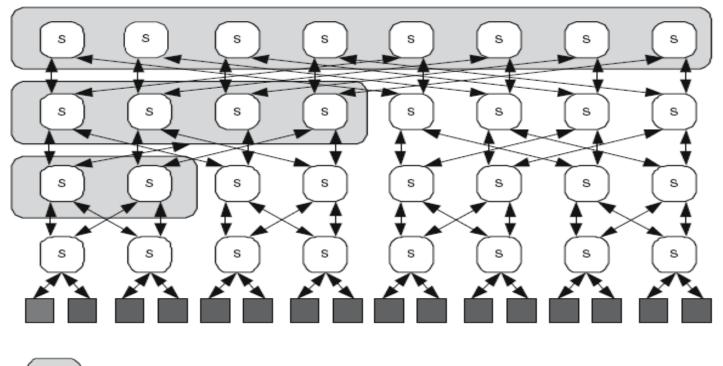

#### TREE-BASED

Fat node represented by a combination of normal nodes

Resource

s

Normal switch or node

Eyal Friedman

## IRREGULAR TOPOLOGY

Eyal Friedman

#### SOFTWARE OPTIMIZATIONS

- extracting parallelism

- coarse grain person

- fine grain compiler

- vendors usually provide models and simulation tools

- task allocation and scheduling

- genetic algorithm is popular for this

- management of inter-processor communication (including memory and i/o management)

- challenging problem no easy solution yet

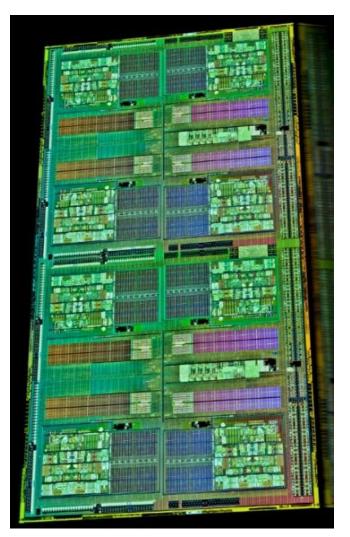

## EXAMPLES OF MP EMBEDDED ARCHITECTURES

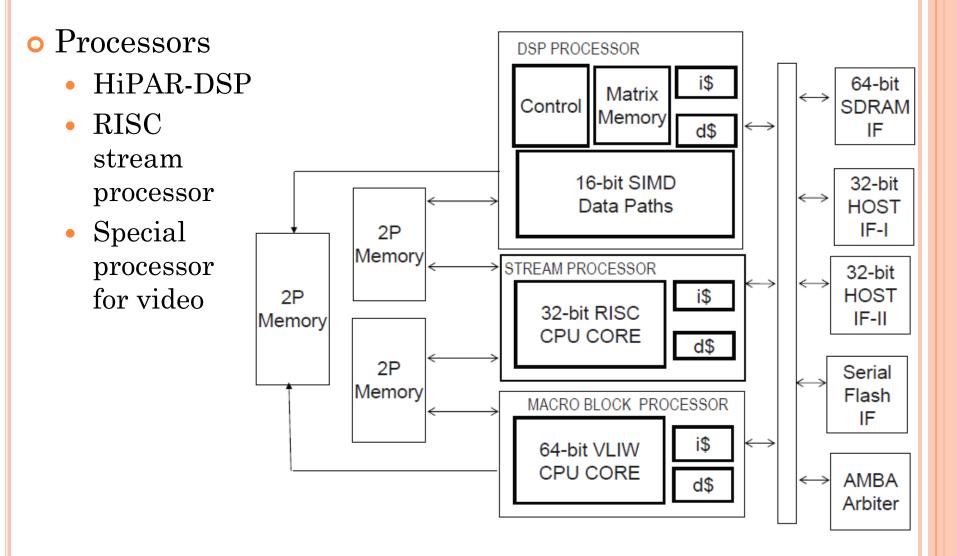

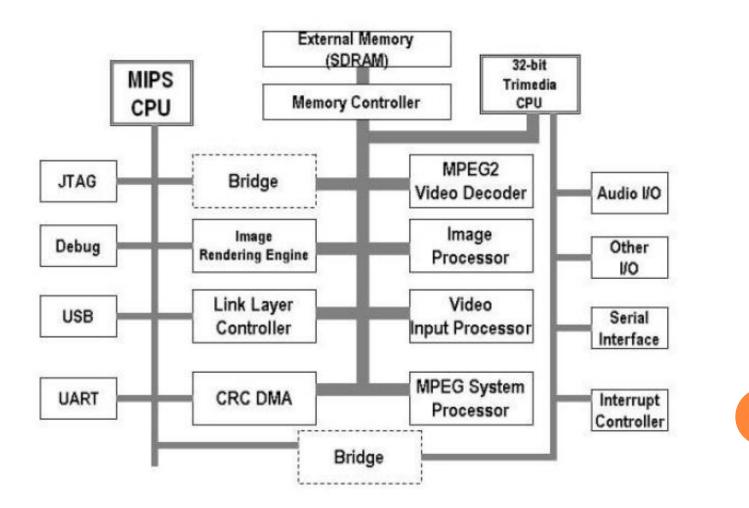

# HIBRID-SOC FOR MULTIMEDIA SIGNAL PROCESSING

#### VIPER MULTIPROCESSOR SOC

• Heterogeneous (For set-top boxes)

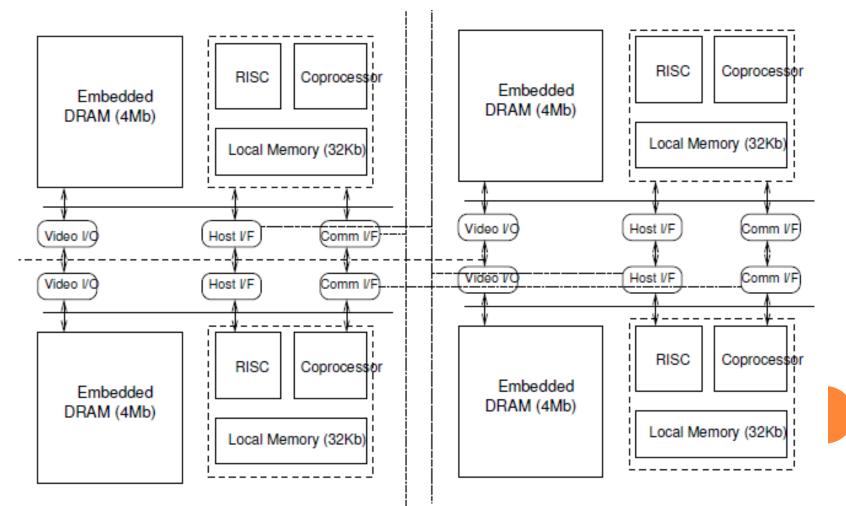

## DEFECT-TOLERANT AND RECONFIGURABLE MPSoC

• Digital video and satellite communication

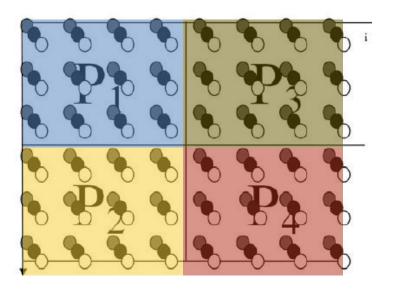

## HOMOGENEOUS MULTIPROCESSOR FOR EMBEDDED PRINTER APPLICATION

Printers process in chunks called "strips" Lends itself to coarse-grained parallelization

| Four Banks of Embedded DRAM<br>(Size = 1MB per bank) |     |           |               |           |     |      |     |  |  |  |  |

|------------------------------------------------------|-----|-----------|---------------|-----------|-----|------|-----|--|--|--|--|

| 256-bit BUS at 256 MHz                               |     |           |               |           |     |      |     |  |  |  |  |

| i\$                                                  | d\$ | <u>19</u> | <del>\$</del> | <u>19</u> | d\$ | i\$  | d\$ |  |  |  |  |

| CPU1                                                 |     | CPU2      |               | CPU3      |     | CPU4 |     |  |  |  |  |

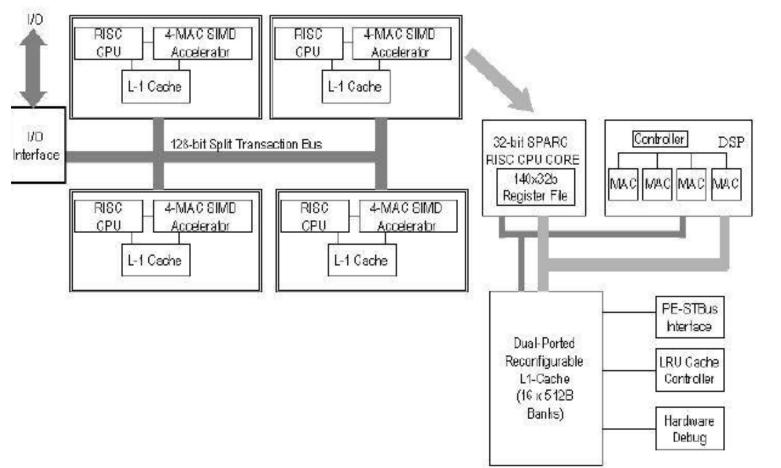

# GENERAL PURPOSE MULTIPROCESSOR DSP

#### • Daytona design built for scalability

• Split transaction bus

## FINAL THOUGHTS

- This book is freely available online (yes, legally)

- Most of the material looks to be applicable to general multi-core architectures

- Good parallel coding practices

- Memory issues

- Design considerations

- Embedded System Examples

- Seem a bit "extra"

## QUESTIONS

Thank You