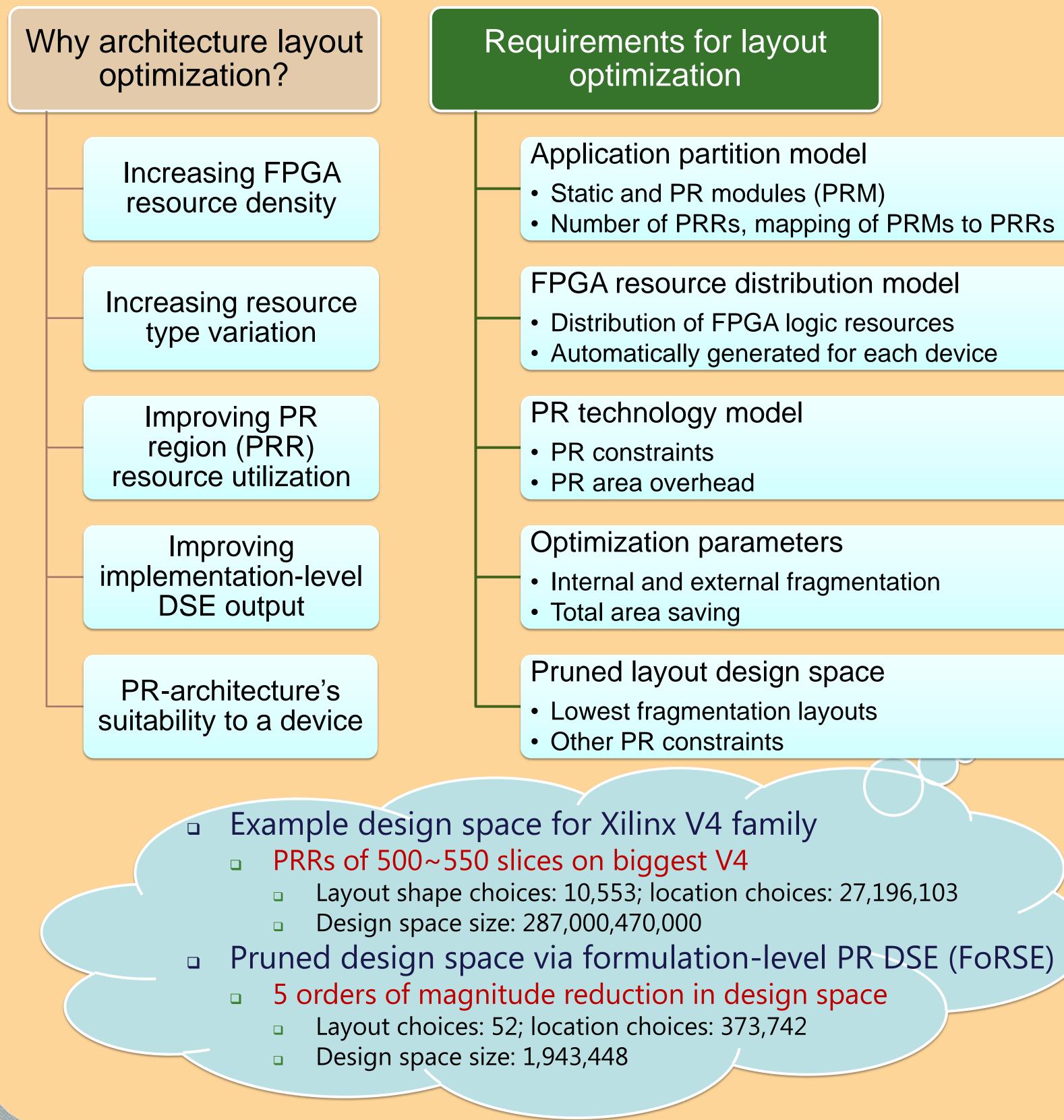

# Introduction

### **Motivations**

- Quantifying partial reconfiguration (PR) benefits is not straightforward

- Many possible PR-architectures and architecture layouts on devices

- Manual and tedious characterization, analysis, and evaluation process

- Early design decision identification reduces design time effort

- Formulation-level analysis affords short design exploration time

### Approach

- PR design space exploration (DSE) in early application development phases

- Evaluate device feasibility for PR-architecture(s) and layouts

- Identify efficient PR-architecture layout(s) and device(s) for slower, more accurate implementation-level DSE Reduces total accumulated implementation-level DSE time

### **Rohit Kumar, Dr. Ann Gordon-Ross**

Number of PRRs, mapping of PRMs to PRRs

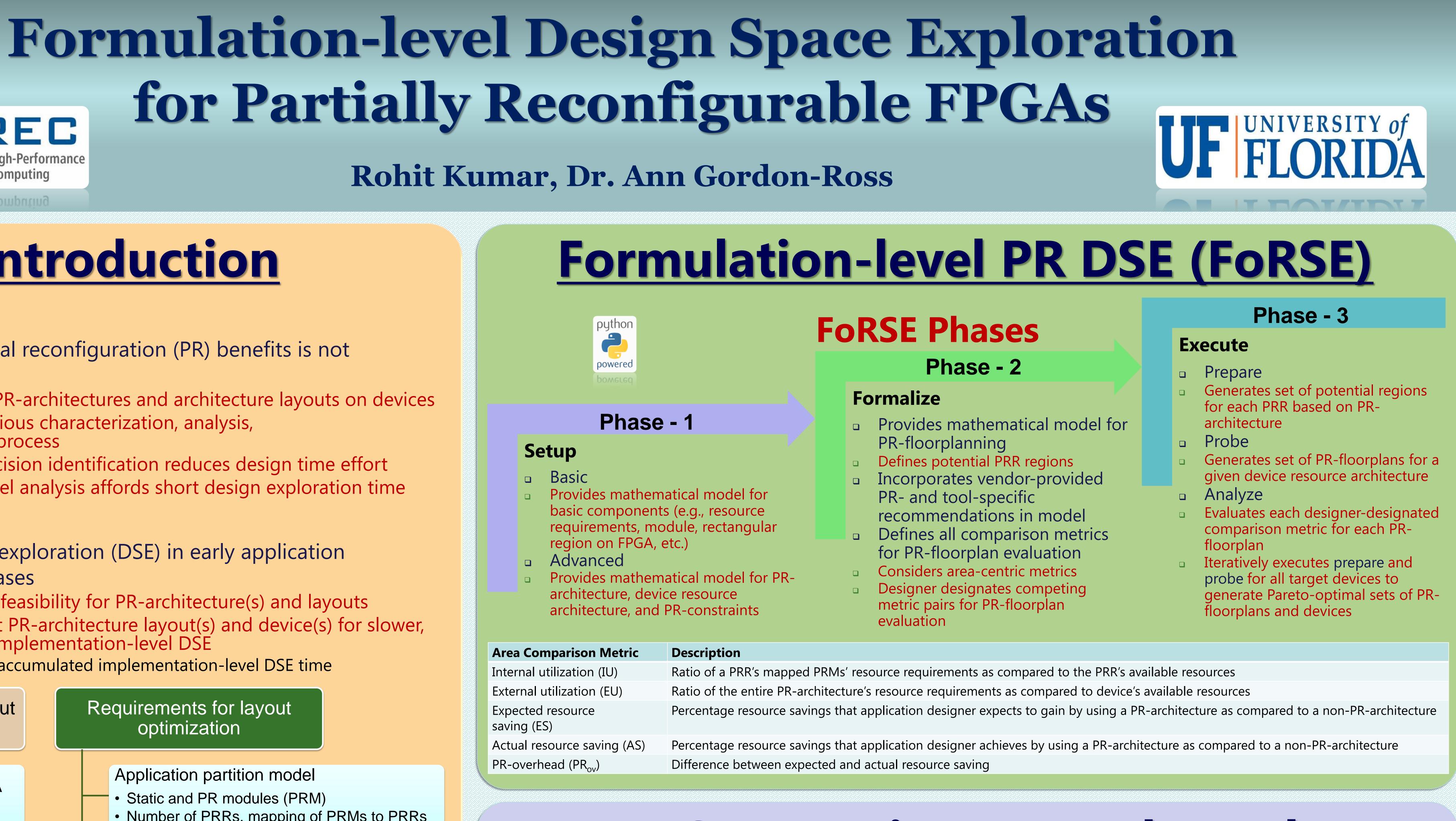

### Setup

- Basic

- region on FPGA, etc.)

- Advanced

- architecture, device resource

| Description   |

|---------------|

| Ratio of a PF |

| Ratio of the  |

| Percentage I  |

| Percentage I  |

| Difference b  |

|               |

### **Input Parameters**

- Sample PR-architecture [Table 1] Estimated resource requirement

- for static and PRMs (M<sub>x,v</sub>)

- $\square$  M<sub>1,1</sub>, M<sub>1,2</sub>, M<sub>1,3</sub> are mapped to PRR '1'

- $M_{2,1}$  and  $M_{2,2}$  are mapped to PRR '2'

- **Table 1:** Sample PR-architecture

| Resource type | e Static | M <sub>1,1</sub> | M <sub>1,2</sub> | M <sub>1,3</sub> | M <sub>2,1</sub> | M <sub>2,2</sub> | <b>PRR '1'</b> | <b>PRR '2'</b> |

|---------------|----------|------------------|------------------|------------------|------------------|------------------|----------------|----------------|

| Slice         | 1365     | 277              | 224              | 195              | 611              | 772              | 277            | 772            |

| BRAM          | 36       | 8                | 4                | 4                | 16               | 16               | 8              | 16             |

| DSP           | 0        | 0                | 2                | 2                | 8                | 8                | 2              | 8              |

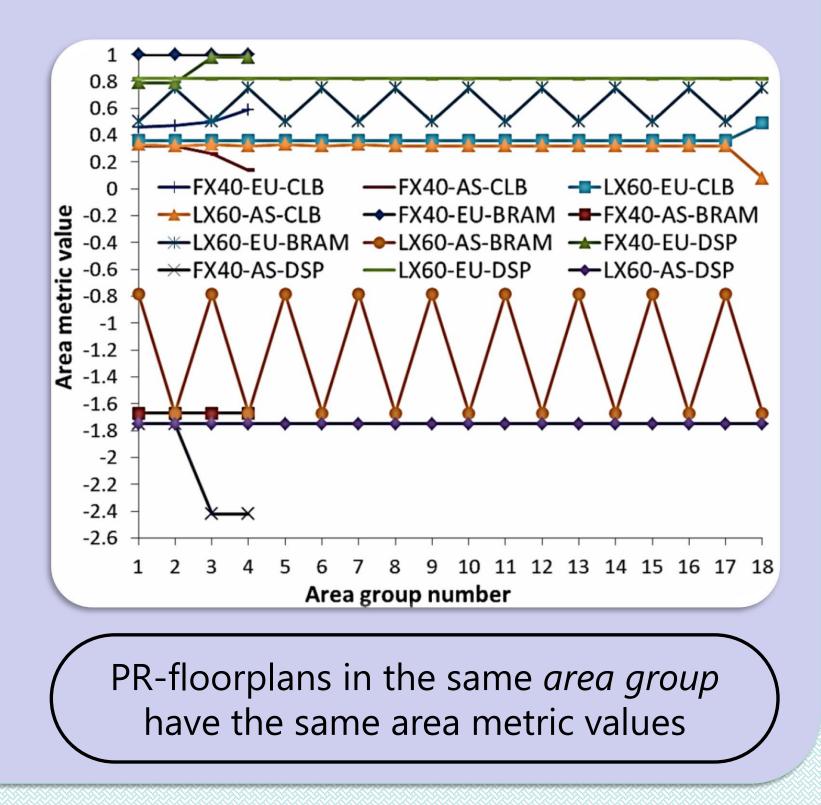

### **Results and Observations**

- Fast DSE (~15 seconds) with little designer effort

- PR-floorplan(s) may require more resources than non-PR-architecture

- Depicted as resource's negative area metric values Savings on one resource may adversely affect others

Reasons: device resource distribution, PR-constraints, and location, shape, and size of PRRs

## **Evaluation Parameters**

- External fragmentation and actual resource savings Calculated individually for each resource type

- Evaluated all Virtex-4 FPGA devices

- Estimated PRM resource requirements do not vary across devices in a family